Actualizado a: 22 de enero de 2024

En el fascinante mundo de las arquitecturas de procesadores de tipo RISC, la rivalidad entre RISC-V vs ARM ha alcanzado bastante importancia, dado que son las dos candidatas a dominar en un futuro próximo. Por eso, vamos a analizar las fortalezas y debilidades de ambas arquitecturas, analizando cómo influyen en la potencia, eficiencia y versatilidad de los dispositivos electrónicos modernos.

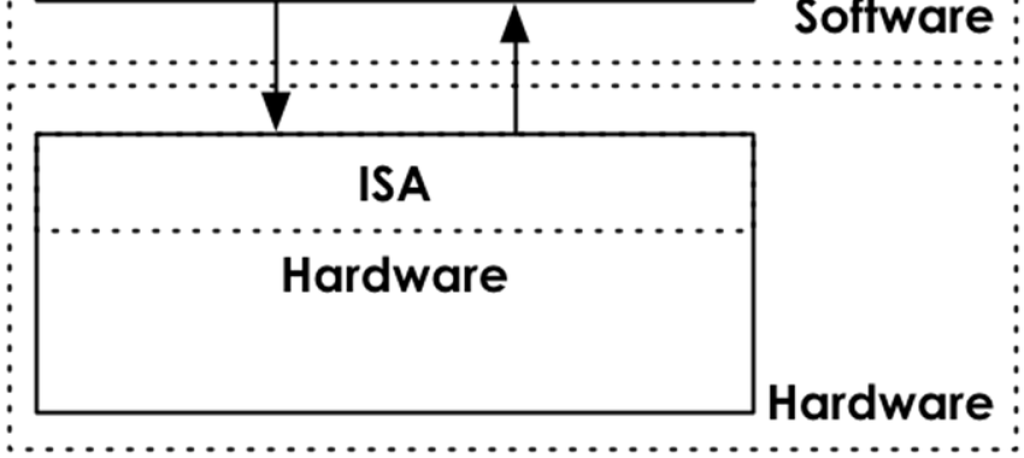

¿Qué es una ISA?

Antes de pasar a la batalla RISC-V vs ARM, primero hay que comprender algunos conceptos básicos necesarios. Por ejemplo, saber qué es una ISA, una microarquitectura, un núcleo IP, etc.

La ISA (Instruction Set Architecture), a veces simplemente llamada arquitectura, se refiere a un conjunto de instrucciones que define las operaciones que un procesador puede llevar a cabo, además, también define el tipo de datos que puede manejar, los registros, tamaño de palabra y los modos de direccionamiento. Aunque siempre se pueden agregar nuevas instrucciones como extensiones, como más adelante veremos.

Es decir, una ISA es un nivel de abstracción que define la interfaz entre el hardware y el software, permitiendo que los programadores escriban código sin tener que preocuparse por los detalles específicos del hardware subyacente. Esta ISA debe tener las suficientes instrucciones para poder ejecutar cualquier software de forma genérica, ya que irán destinadas a las CPUs de propósito general en la mayoría de los casos. Por ejemplo, cuando un programador escribe un código fuente de un programa cualquiera, una vez compilado, pasará a formato binario, con las instrucciones en código máquina necesarias para que la CPU al ejecutarlas pueda hacer funcionar este software.

Por ejemplo, esto es un sencillo código fuente escrito en lenguaje C que ejecuta un programa simple para mostrar en pantalla un mensaje «Hola Mundo!», pero este código fuente es genérico, podría funcionar en cualquier ISA:

#include <stdio.h>

int main() {

printf("Hola Mundo!\n");

return 0;

}

Sin embargo, una vez pasamos este código a lenguaje ensamblador, podemos tener un ASM para la arquitectura x86-64 tipo:

section .data

hello db 'Hola Mundo!', 0

section .text

global _start

_start:

; Escribe el mensaje en la consola

mov rax, 1 ; syscall para sys_write

mov rdi, 1 ; descriptor de archivo: stdout

mov rsi, hello ; puntero al mensaje

mov rdx, 12 ; longitud del mensaje

syscall

; Salir del programa

mov rax, 60 ; syscall para sys_exit

xor rdi, rdi ; código de salida 0

syscall

O para la arquitectura ARM que sería de este otro modo:

.data

hello: .asciz "Hola Mundo!\n"

.text

.global _start

_start:

// Escribe el mensaje en la consola

mov x8, 64 // syscall para sys_write

mov x0, 1 // descriptor de archivo: stdout

ldr x1, =hello // dirección del mensaje

ldr x2, =13 // longitud del mensaje

svc 0

// Salir del programa

mov x8, 93 // syscall para sys_exit

mov x0, 0 // código de salida 0

svc 0

O por ejemplo, en ASM para RISC-V sería como este:

# Sección de datos

.data

hello_string: .asciiz "Hola, mundo\n"

# Sección de texto

.text

.globl _start

_start:

# Llamada al sistema para escribir en la salida estándar

li a0, 1 # Descriptor de archivo: STDOUT

li a1, hello_string # Dirección de la cadena

li a2, 13 # Longitud de la cadena

li a7, 64 # Código de la llamada al sistema para escribir (64 en RISC-V)

ecall # Realizar la llamada al sistema

# Llamada al sistema para salir

li a7, 93 # Código de la llamada al sistema para salir (93 en RISC-V)

li a0, 0 # Código de salida

ecall # Realizar la llamada al sistema

Por tanto, el código máquina de un programa y otro varía, el procesador x86 no comprendería el binario compilado para ARM, y el procesador ARM no comprendería el binario compilado para x86…

Dicho de otro modo, la ISA especifica el repertorio de operaciones que una CPU puede ejecutar, como puede ser ADD para sumar datos, SUB para restar, MUL para multiplicar, DIV para dividir, y otras muchas operaciones tanto a nivel de datos, como para acceso a memoria, operaciones a nivel lógico y no solo aritmético, etc. Es decir, es el lenguaje que la CPU entenderá y al cual se tienen que traducir el software para que funcione en una determinada máquina.

Existen diversas ISAs, siendo las más conocidas las arquitecturas x86, ARM, MIPS, Power ISA, RISC-V, SPARC, entre otras. Cada ISA tiene su propio conjunto único de instrucciones y reglas para su ejecución. Los compiladores traducen el código fuente de alto nivel a código de máquina específico de la ISA que será ejecutado por el procesador. Por este motivo, un programa compilado para un x86 no es compatible con un chip Arm, o viceversa, ya que cada ISA es un lenguaje diferente que el hardware debe entender.

La mayoría de las ISAs que se emplean en la actualidad fueron desarrolladas hace décadas, aunque han tenido sus actualizaciones y han ido agregando extensiones para mejorar el rendimiento para las cargas de trabajo actuales. Sin embargo, muy pocas son realmente nuevas. Un caso de arquitectura joven y diseñada desde cero para los tiempos modernos es RSIC-V.

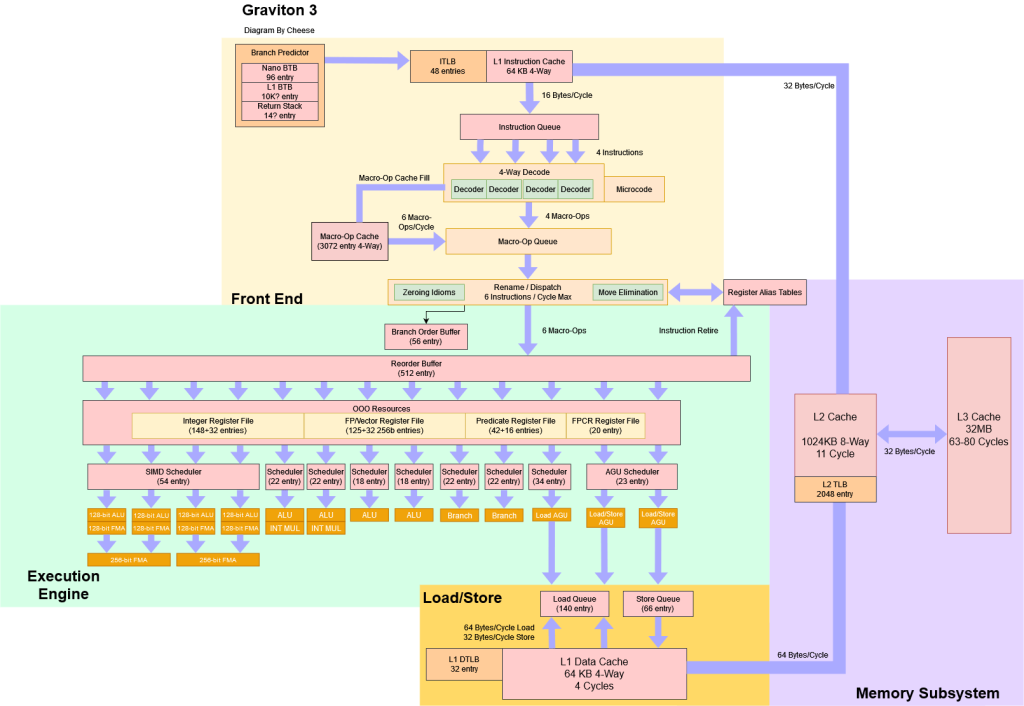

Microarquitectura

La microarquitectura de una CPU se refiere a la implementación interna específica de una arquitectura o ISA. Es decir, el diseño que se crea para poder desarrollar esa ISA. En otras palabras, la microarquitectura describe la estructura interna de la CPU, incluyendo cómo se gestionan y ejecutan las instrucciones, cómo se realiza la ejecución fuera de orden (si es aplicable), cómo se manejan los registros, cómo se accede y se gestiona la memoria caché, y otros detalles a nivel de circuitos y lógica interna.

Por ejemplo, dos ejemplos de microarquitecturas actuales son la AMD Zen 4 y la Intel Meteor Lake, tanto una como otra pueden ejecutar una ISA x86-64. Sin embargo, son diferentes, creadas por diferentes compañías. Esto quiere decir que para una misma ISA puede haber muchas microarquitecturas diferentes, como hemos visto a lo largo de la historia. Sin embargo, una microarquitectura no puede funcionar para otra ISA diferente, ya que para ello habría que diseñarla específicamente para esa otra ISA. Por ejemplo, una microarquitectura Qualcomm Kryo está diseñada para la ISA ARM, y no podría entender las instrucciones de una x86 o de cualquier otro tipo.

Núcleo IP

Un núcleo IP (Propiedad Intelectual, por sus siglas en inglés) se refiere a un bloque de diseño de hardware que ha sido predefinido por una compañía, es decir, es la implementación de la microarquitectura para una ISA específica. Esencialmente, un núcleo IP es una unidad funcional completa que puede ser integrada en un diseño de chip más amplio sin necesidad de recrear o diseñar esa funcionalidad desde cero.

Algunas compañías solo diseñan núcleos para sí mismas, y no entregan la propiedad intelectual de estos núcleos a terceros. Es el caso, por ejemplo, de Intel o Apple, mientras que otras compañías permiten licenciar estos núcleos para que terceros los puedan usar en sus diseños, sin necesidad de crear ellos la microarquitectura desde cero. Un ejemplo de esta otra forma de licenciar núcleos la tenemos en Arm y también en algunas compañías como SiFive, de la que más adelante comentaré, al estar relacionada como RISC-V.

Arquitectura abierta vs arquitectura cerrada

Para comprender mejor la batalla RISC-V vs ARM, es importante conocer qué es una ISA cerrada o propietaria y una ISA abierta o de código abierto:

- Una ISA cerrada o propietaria se refiere a una arquitectura de conjunto de instrucciones cuyos detalles internos y especificaciones están controlados y mantenidos por una entidad específica, como una empresa. Los detalles exactos del diseño y funcionamiento de la arquitectura son propiedad exclusiva de esa entidad y, a menudo, están protegidos por derechos de autor o patentes. Los desarrolladores y fabricantes de hardware deben obtener licencias o permisos para implementar procesadores que sigan dicha ISA. Ejemplos de este tipo de ISA son la x86 que se emplea por Intel, AMD, etc., y que fue propiedad de Intel, por lo que el resto de compañías debían pagar regalías a la compañía para poderla usar, aunque AMD tenía un acuerdo de licencias cruzadas para poderla usar. Es más, AMD se encargó de diseñar la AMD64, lo que Intel ha denominado EM64T, es decir, la extensión de 64-bit o x86-64, por lo que ahora es AMD la que tiene esta propiedad. Cualquiera que quiera usar la ISA, tendrá que pagar a estas compañías. Otro caso de este tipo de ISA cerrada es ARM, creada por Arm y que nadie puede usar sin una licencia, es decir, pagando a esta compañía para crear chips basados en ella. Por ejemplo, Apple debe pagar por la ISA Arm para sus chips, Qualcomm hace lo mismo para los suyos, etc.

- Una ISA de código abierto es aquella cuyas especificaciones están disponibles públicamente, y cualquiera puede implementarla y contribuir a su desarrollo. No hay restricciones significativas sobre quién puede usar o contribuir al diseño. Esto fomenta la colaboración y la innovación en el desarrollo de hardware compatible. Ejemplos de este tipo son las ISA MIPS, recientemente liberada, o la OpenPOWER de IBM, que también ha sido liberada y ahora es parte de la OpenPOWER Foundation. Y, por supuesto, la más conocida de todas es la RISC-V. En estos casos, cualquiera podría usar la ISA en sus diseños sin necesidad de pagar, ya que están bajo licencias libres como pueda ser BSD, o similares. Como sabrás, OpenPOWER es la ISA Power ISA usada por IBM y que ahora ya no es cerrada.

Las ISA de código abierto a menudo se consideran beneficiosas para la innovación y la competencia, ya que permiten una mayor flexibilidad y colaboración en el desarrollo de hardware. Y ahorran a las empresas que las usan grandes cantidades de dinero en royalties.

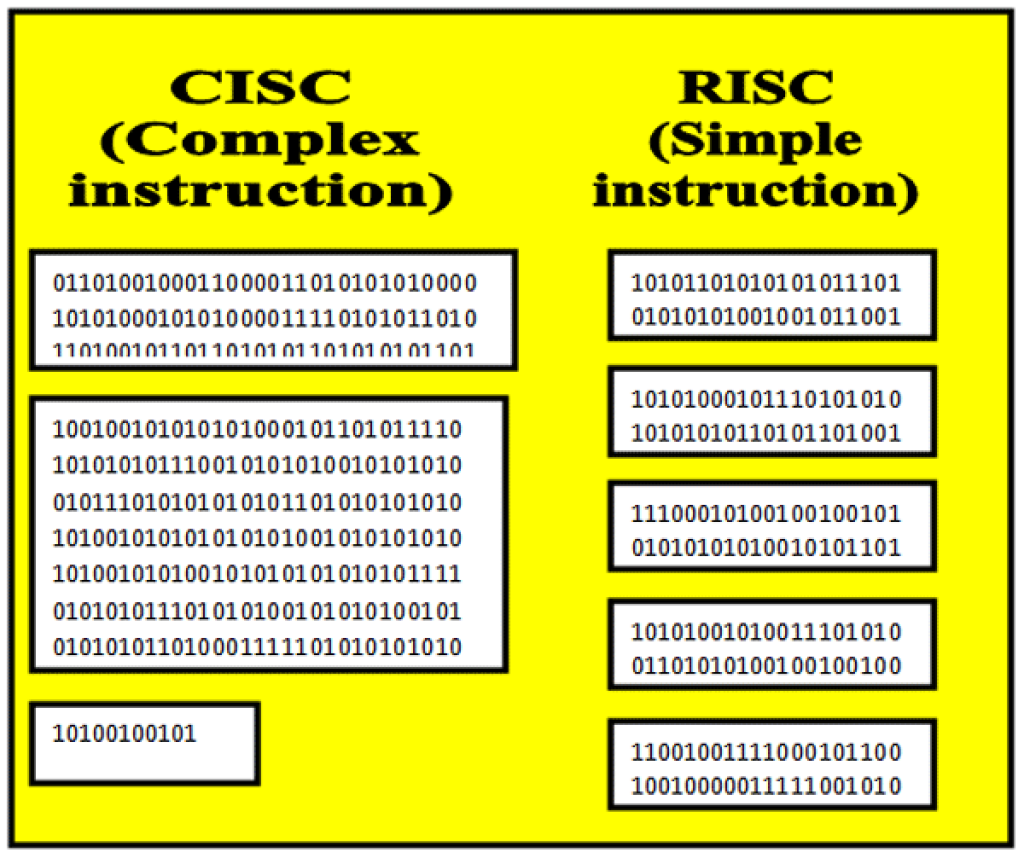

RISC vs CISC

Dado que ambas ISAs que tratamos en esta comparativa RISC-V vs ARM son de tipo RISC, es importante conocer qué es RISC (Reduced Instruction Set Computing) y qué diferencias tiene con la CISC (Complex Instruction Set Computing). Ejemplos de RISC los tenemos en ARM, RISC-V, MIPS, SPARC, POWER, etc., mientras que ejemplos de CISC los tenemos en x86, Z/Architecture, etc. Generalmente, las CISC son las más viejas, mientras que RISC fue un paradigma que llegó más tarde. Sin embargo, hay que decir que las implementaciones CISC actuales funcionan a nivel físico como una RISC, para aprovechar las ventajas de ésta. Por ejemplo, Intel y AMD con su conjunto x86 CISC, a nivel de hardware sus CPUs trabajan como una RISC, traduciendo estas instrucciones grandes de tipo CISC a unas instrucciones más simples al estilo RISC denominadas microoperaciones.

Para diferenciar entre RISC y CISC y ver las ventajas y desventajas de cada una, vamos a irlas comparando punto por punto:

- Complejidad de instrucciones:

- RISC: se caracteriza por un conjunto de instrucciones reducido y simple. Las instrucciones suelen realizar operaciones básicas y se diseñan para ejecutarse en un solo ciclo de reloj. Además, las instrucciones son de longitud fija, y cuentan con pocos modos de direccionamiento.

- CISC: presenta un conjunto de instrucciones más extenso y complejo, con operaciones que pueden requerir múltiples ciclos de reloj. La longitud de estas instrucciones puede variar de unas a otras.

- Complejidad del hardware:

- RISC: el hardware asociado con las instrucciones es más simple, ya que cada instrucción es más básica y requiere menos circuitos de control. Por tanto, implementar la microarquitectura es más fácil.

- CISC: se asocia con hardware más complejo para decodificar y ejecutar instrucciones más elaboradas.

- Eficiencia de ejecución:

- RISC: al ser instrucciones más simples y cortas, los procesadores RISC ejecutan estas operaciones de forma más rápida, es decir, necesitan menos ciclos de reloj. Además, se puede elevar la frecuencia de reloj más que en diseños CISC.

- CISC: al ser instrucciones más pesadas, se toma más tiempo en poderlas ejecutar. Incluso los diseños con traducción dinámica de CISC a RISC, como he explicado en el caso de Intel y AMD, esto implica un mayor esfuerzo por parte del hardware, ya que mediante el microcódigo tienen que traducir cada instrucción CISC en varias microoperaciones.

- Optimización de la pipeline:

- RISC: el diseño favorece la implementación de pipelines más eficientes, permitiendo mayor grado de paralelismo, permitiendo iniciar la siguiente instrucción antes de que la anterior haya terminado. Esto mejora el rendimiento.

- CISC: esto es algo más complicado, aunque con las técnicas que he mencionado es posible.

- Consumo de energía:

- RISC: al ser un diseño más simple de hardware, el consumo es menor por lo general. Esto permite una gran eficiencia en estos chips.

- CISC: al ser más compleja, el consumo puede ser algo superior en comparación.

- Longitud de programas:

- RISC: dado que las instrucciones son más simples, para ejecutar un mismo programa, se necesita un código más largo, con más instrucciones para hacer lo mismo.

- CISC: al ser instrucciones complejas, una misma instrucción podría hacer lo mismo que varias RISC, por lo que los códigos son más cortos en este sentido.

- Carga de compilación:

- RISC: en estos diseños la optimización recae más en el compilador. Esto quiere decir que tendremos compiladores más complejos y hardware más simple.

- CISC: en este diseño la optimización recae más del lado del hardware. Por tanto, tendremos compiladores más simples, pero hardware más complejos.

¿Qué es ARM?

Arm (ahora propiedad de la japonesa Softbank) es una empresa líder en el diseño y licencia de chips, especializada en la arquitectura ARM, cuyas siglas provenían de Advanced RISC Machine. En sus inicios, esta arquitectura diseñada en Reino Unido era simplemente para ordenadores Acorn, aunque poco a poco se iría expandiendo gracias a su relación rendimiento/eficiencia en el ámbito de los embebidos y dispositivos móviles, hasta ganar importancia también en servidores, HPC e incluso adentrarse en el ámbito de los PCs.

Gracias a esto, su ecosistema es bastante rico, existe mucho software compilado compatible con esta plataforma y también hardware compatible. Incluso han soportado estándares típicos de x86 como puede ser ACPI, UEFI, etc. En cuanto a sistemas operativos, tenemos también variedad de ellos compatibles, como puede ser GNU/Linux (también ChromeOS y Android), Windows, FreeBSD, iOS/iPadOS, macOS, etc.

ARM, que originalmente significaba Acorn RISC Machine, fue creado por Acorn Computers en la década de 1980. En 1990, se formó la empresa conjunta Advanced RISC Machines Ltd. (ahora ARM Holdings) entre Acorn Computers, Apple y VLSI Technology. Los primeros procesadores ARM, como ARM1 y ARM2, se utilizaron en las computadoras Archimedes y ganaron popularidad con el procesador ARM610 seleccionado por Apple para su asistente digital personal Newton en 1993.

Como he comentado, ARM es una ISA tipo RISC que se ha destacado por su eficiencia y simplicidad, además por su alto rendimiento como han demostrado muchos de sus diseños. Aunque Arm es la que diseñó la ISA y ahora también se encarga de diseñar las microarquitecturas y los núcleos IP para licenciarlos a terceros, hay que decir que también se puede licenciar al ISA. De hecho, Arm cuenta con una oferta flexible, por ejemplo:

- Licenciar ISA: Arm permite pagar por usar la ISA y que sea una empresa tercera la que se encargue de desarrollar la microarquitectura desde cero. Es el caso de los diseños como los Apple A-Series y M-Series, que están diseñados por Apple.

- Licenciar núcleos IP: también permite pagar por usar núcleos IP ya diseñados por la propia Arm para agregarlos a un SoC o ASIC por un tercero, como los núcleos Cortex-A Series, Cortex-M Series, Cortex-R, Neoverse (especiales para servidores y HPC), etc. Por ejemplo, los SoCs de Mediatek, Qualcomm, Samsung, y otros muchos, usan núcleos licenciados de este tipo, por lo que solo tienen que agregar estos núcleos IP en sus diseños en la cantidad que deseen, evitando tener que diseñar la microarquitectura desde cero. Además, Arm también permite hacer uso de núcleos IP a los que se le puede modificar la microarquitectura para personalizarlos, esto también es otro tipo de licencia que se puede pagar. Un ejemplo de este caso los tenemos en algunas CPUs basadas en ARM para HPC, o en los núcleos Kryo de los Qualcomm Snapdragon que era una microarquitectura modificada por Qualcomm, aunque basada en los Cortex-A como base. Otros ejemplos basados en los Arm Neoverse son los procesadores Fujitsu A64FX, Ampere Altra, AWS Graviton, etc.

Esta flexibilidad es la que le ha permitido tener un modelo exitoso en el mercado. Además de la eficiencia y el rendimiento conseguidos. Se calcula que actualmente se han usado más de 180.000 millones de diseños Arm para todo tipo de sistemas. Y cada vez son más populares y llegan a más sectores del mercado… pero se han topado con un gran contrincante, como es RISC-V.

¿Qué es RISC-V?

RISC-V es una ISA de estándar abierto, también tipo RISC, desarrollada en la Universidad de California, Berkeley, que ha captado la atención de importantes empresas. A diferencia de otras ISA, RISC-V permite una expansión del conjunto de instrucciones según las necesidades del chip, comenzando con 47 instrucciones base, y pudiendo ir agregando módulos según sea necesario, sin tener que arrastrar las dependencias anteriores como ocurre de forma tan evidente en x86 y otras arquitecturas. Además, al ser décadas más reciente que todas las demas, se ha diseñado pensando en las necesidades actuales, lo cual es una gran ventaja.

Iniciado en 2010, RISC-V es una ISA de arquitectura abierta, libre de licencias y regalías, bajo licencia BSD. De ella se dice que es como el fenómeno Linux fue en su momento en el ámbito del software, pero en el hardware. De hecho, cada vez tiene más y más interés, y se piensa que es la arquitectura del futuro, incluso superndo a Arm.

En su creación intervinieron personas como David Patterson, que junto con John L. Hennessy, son los padres de RISC, cuando diseñaron el Berkeley RISC I y Stanford MIPS respectivamente. De hecho, RISC-V viene de ser la quinta implementación tras el RISC-I, RISC-II, SOAR/VLSI-BAM y SPUR.

Al ser una ISA de código abierto, no hay que pagar por usarla, una gran ventaja para las compañías que deseen desarrollar microarquitecturas basadas en ella. No obstante, si se prefiere la «comodidad» del modelo Arm, consiguiendo núcleos IP ya acabados, existen empresas que han surgido en torno a RISC-V como es SiFive, que también permite licenciar sus núcleos IP para integrarlos en chips de terceros. Así que, en este sentido, tenemos lo mejor de ambos mundos.

Por otro lado, RISC-V tiene muchas semejanzas con ARM, incluida esa magnífica relación rendimiento/eficiencia energética que la hace tan atractiva. De hecho, primero se creó la fundación paraguas RISC-V Foundation, bajo la Linux Foundation, y más tarde como RISC-V International, la cual cuenta con miembros de la categoría de: AMD, Intel, Qualcomm, NVIDIA, Google, Seagate, Western Digital, SiFive, Infineon, IBM, Mediatek, MIPS Technologies, Nokia, Raspberry Pi Foundation, Texas Instruments, STMicroelectronics, Sony, Siemens, Renesas, Arduino, Analog Devices, Samsung, Nokia, Synopsis, Raytheon, SUSE, Canonical, IMEC, ESA, De-RISC Project, FreeBSD Project, Cadence, Rambus, Meta, NXP, Alibaba, y un enorme listado de miembros muy importantes de la industria.

Actualmente no cuenta con un ecosistema tan rico como Arm, ya que al ser más joven, solo encontramos por el momento compatibilidad con el sistema operativo GNU/Linux y recientemente también Android lo será. Mientras que del lado del hardware paso algo similar, aunque poco a poco están siguiendo los pasos de Arm para soportar los mismos estándares, como UEFI, etc.

Al igual que Arm, también admite extensiones de la ISA mediante módulos, con capacidad para hacer uso de instrucciones tipo SIMD de mayor longitud para acelerar cálculos vectoriales. Algo importante para el alto rendimiento.

Diferencias y similitudes RISC-V vs ARM

Una vez comprendemos mejor qué es ARM y qué es RISC-V, ahora vamos a ver algunas similitudes y diferencias que también nos ayudarán en la comprensión de nuestra comparativa RISC-V vs ARM:

- RISC-V vs ARM: similitudes

- Tanto RISC-V como ARM son RISC.

- RISC-V y ARM utilizan la arquitectura de carga-almacenamiento (Load/Store o L/S), lo que significa que los datos se cargan desde la memoria, se procesan en la CPU y luego se devuelven a la memoria.

- Ambos RISC-V y ARM admiten conjuntos de instrucciones de 32 o 64 bits, además de extensiones tipo SIMD de 128-bit o más.

- Ambos pueden usarse en diseños SoC, FPGA, ASICs, y para sectores desde los embebidos o empotrados, hasta los PCs, servidores y HPC, así como dispositivos móviles.

- RISC-V vs ARM: diferencias

- RISC-V es una arquitectura de código abierto, mientras que ARM es propietaria. Esto significa que cualquier diseñador que desee incluir una CPU ARM en su diseño (por ejemplo, un SoC) debe pagar regalías a Arm, y estas licencias suelen ser caras, de decenas de miles de euros o centenares de miles de euros. RISC-V, por otro lado, es de código abierto y no requiere regalías ni licencias, es decir, cualquiera que desee usarla es gratuita. Además, como he comentado, en Arm tenemos posibilidad de usar núcleos IP ya creados por ingenieros pagando por ellos, y en RISC-V pasa algo parecido con núcleos IP como los que desarrolla SiFive.

- El soporte de RISC-V es mínimo, mientras que el soporte de ARM es extenso. Debido a que RISC-V es una plataforma de CPU relativamente nueva, hay un soporte de software y entorno de desarrollo muy limitado. ARM, por otro lado, ofrece una enorme comunidad en línea, un sistema de soporte y bibliotecas para ayudar a los diseñadores a dirigirse a una amplia gama de dispositivos, incluyendo microcontroladores, microprocesadores para dispositivos móviles, embebidos, PCs, servidores, etc. No obstante, RISC-V está avanzando a pasos agigantados, y es probable que en unos años ya puedan estar a la par.

- La endianness de RISC-V es little endian, pero la endianness de ARM es bi-endian. Little Endian es un formato donde el byte menos significativo (el byte más pequeño) de un dato se almacena en la dirección de memoria más baja, y los bytes más significativos siguen en direcciones de memoria crecientes. Es como leer un número de izquierda a derecha. En big endian, el byte más significativo (el byte más grande) se almacena en la dirección de memoria más baja, y los bytes menos significativos siguen en direcciones de memoria crecientes. Es como leer un número de derecha a izquierda.

RISC-V vs ARM: comparativa

Llegados a este punto, es el momento de analizar la comparativa RISC-V vs ARM para ver quién gana en casa caso. Para eso, vamos a ir punto a punto:

Rendimiento

La comparación entre las arquitecturas RISC-V vs ARM abarca varios aspectos, considerando factores como generaciones de núcleos, eficiencia y modelos específicos. Uno de los factores más detereminantes cuando se trata de núcleos de procesamiento es su rendimiento. En este sentido, no hay un claro ganador, ya que el rendimiento no depende tanto de la ISA sino más bien de la microarquitectura. Ambos han demostrado que pueden aportar gran rendimiento, aunque RISC-V está sorprendiendo especialmente con algunos diseños en CoreMark/MHZ. Además, pese a su juventud, algunos diseños de alto rendimiento de RISC-V ya igualan o superan a los Arm similares.

Es más, los núcleos RISC-V han demostrado ser incluso más pequeños que los Arm, y eso que éstos ya eran más compactos que los x86, etc. Esto es positivo para poder integrar mayor cantidad de núcleos en una misma superficie del chip. En este caso, usando el mismo silicio, RISC-V saldría ganando, con una densidad de cómputo mayor.

Los núcleos de uno y otro apuntan muy alto en el futuro, y muchas empresas deberían estar preocupadas, como las que se centran en x86, de hecho, ya han dado un paso al interesarse por estos diseños de cara al futuro. Esto dice mucho de Arm y de RISC-V. Y, aunque no hay un claro ganador, y pese a que Arm tiene algunos diseños muy poderosos en la actualidad, RISC-V está apuntando muy alto, así que es cuestión de tiempo…

Eficiencia energética

Otra de las cosas importantes en cuanto a la batalla RISC-V vs ARM es la eficiencia energética, ya que de ello no solo dependerá el consumo, también el ahorro en centros de datos y las capacidades de integrar más o menos núcleos en un mismo chip o en empaquetados 3D por las limitaciones de potencia.

La comparación de eficiencia energética entre las arquitecturas RISC-V y ARM revela datos intrigantes. Por un lado, tenemos que RISC-V destaca por su simplicidad y modularidad, potenciando eficiencia en sistemas integrados, IoT y dispositivos con batería. La ISA RISC-V permite procesadores con pequeña huella de silicio, reduciendo consumo de energía. Características como instrucciones de 32 bits y extensión RV32C contribuyen a la eficiencia energética.

Por otro lado tenemos ARM, con un enfoque clave en eficiencia energética desde sus inicios, preferido en aplicaciones móviles e integradas. Y las familias de procesadores, como Cortex-A, Cortex-R y Cortex-M, optimizadas para diferentes objetivos de potencia y rendimiento, como CPUs de propósito general, microcontroladores, etc. Y es verdad que destacan por su rendimiento/vatio, pero no están demasiado lejos de RISC-V.

La conclusión que se saca de aquí es que ARM destaca con técnicas refinadas de gestión de energía y núcleos especializados, respaldado por su amplio ecosistema y adopción en la industria. Aunque RISC-V promete con su potencial de personalización, su naturaleza abierta requiere mayor inversión de tiempo y recursos para aprovechar completamente sus capacidades de ahorro de energía.

Conclusión

Aunque en muchas cosas estén bastante igualados, RISC-V tiene una clara ventaja, y es que al no depender de una empresa, como ARM, la cantidad de apoyos que está recibiendo es mucho mayor. Y su licencia de código abierto es un plus muy a tener en cuenta. Por tanto, pese a estar por detrás en cuanto al ecosistema disponible en la actualidad, esto es solo cuestión de tiempo que cambie. Así que Arm debe estar temblando… o debería.

Además, RISC-V, incluso en el caso de empatar en rendimiento, eficiencia energética, y ecosistema, seguiría teniendo una gran ventaja que Arm no tiene, y es el hecho de ser de código abierto como he comentado. Ya que esto va a atraer a muchas más empresas que no desean pagar regalías por usar la ISA, lo que en un futuro no muy lejano dará lugar a diseños muy variados y nutrirán al ecosistema. Y, si se quiere seguir el ejemplo de Arm, como ya he comentado, existen empresas como SiFive que licencian sus núcleos IP para facilitar las cosas a terceros.

Arm podría seguir los pasos de otras como OpenPOWER y MIPS, volviéndose también de código abierto. Pero lo cierto es que las ganancias de Arm dependen de su modelo de negocio actual, por lo que esto no tendría sentido. Es más, la gran amenaza para Arm es que alguna empresa compre esta compañía. Ahora en manos de SoftBank, pero estuvo a punto de ser adquirida por NVIDIA. Si esto ocurriese, dicha empresa tendría el control para hacer con ella lo que quisiera, incluso agregar instrucciones para beneficiarse a ella misma, aunque ello suponga perjudicar a los demás, o incluso terminar con el modelo de licenciamiento. Mientras que esto jamás sucederá a RISC-V, que siempre será abierta e independiente, por lo cual no estará bajo el control de ninguna empresa o gobierno. Esto quiere decir que tampoco se podrán poner sanciones como las que hemos visto con Arm en China.

Otro detalle importante a favor de RISC-V es que gracias a su modularidad y juventud, pensada para las actuales cargas y diseños, está siendo muy considerada para el uso, por ejemplo, en DSA, o aceleradores de cargas específicas. Ago en lo que Arm no ha calado. Ejemplo de ello son empresas como Tenstorrent, como el proyecto EPI/SiPearl europeo con acleradores basados en RISC-V, etc. Por ejemplo, estos DSA están teniendo mucho interés en aplicaciones como la inteligencia artificial. Algo en lo que las antiguas ISA no estaban tan preparadas, y para acelerar han tenido que implementar NPUs o similares como hemos visto, para trabajar mejor con datos de 8-bit o 16-bit que son los más empleados por este tipo de cargas.

Para los que aún no sepaís qué es un DSA, decir que son las siglas de Domain Specific Accelerator, en español, un Acelerador Específico de Dominio, es un tipo de hardware diseñado para acelerar tareas específicas en lugar de realizar propósitos generales. Estos aceleradores están optimizados para cargas de trabajo particulares o dominios de aplicaciones específicos, como aprendizaje profundo, procesamiento de señales, procesamiento de imágenes, análisis de datos financieros, etc. Es decir, contrastan con las CPUs de propósito general y la GPGPU, aunque también forman parte de las nuevas arquitecturas heterogéneas que están proliferando.

Existen varias razones por las cuales los DSAs están ganando importancia:

- Eficiencia energética: se diseñan para tareas específicas, lo que permite una optimización extrema para esa tarea en particular. Esto a menudo conduce a una mayor eficiencia energética en comparación con los procesadores de propósito general que pueden tener que realizar una variedad de tareas. Esto supone grandes mejoras si se tienen en cuenta métricas como bit/w transferido o rendimiento/vatio.

- Mejor desempeño: al estar especializados en un dominio particular, los DSAs pueden superar en rendimiento a las unidades de procesamiento general. Pueden realizar cálculos especializados de manera más rápida y eficiente en comparación con los diseños de propósito general. Muchas aplicaciones modernas, como el aprendizaje profundo, el análisis de grandes conjuntos de datos, el procesamiento de gráficos, etc., tienen requisitos de cómputo intensivo y son ideales para la aceleración con DSAs especializados.

- Paralelismo: muchas cargas de trabajo específicas pueden aprovechar el paralelismo de manera más eficiente que las tareas de propósito general. Los DSAs pueden diseñarse para aprovechar este paralelismo y, por lo tanto, aumentar significativamente el rendimiento.

- Escalabilidad: al centrarse en tareas específicas, los DSAs pueden ser diseñados para ser escalables en función de la carga de trabajo específica. Esto permite construir sistemas altamente eficientes para aplicaciones concretas.

En definitiva, RISC-V es el futuro…