Actualizado a: 22 de enero de 2024

Amazon también se ha adentrado en el sector de la tecnología, y no solo el de la venta online. Y lo han hecho con fuerza, con AWS (Amazon Web Services), una de las plataformas de la nube más competitivas y también han querido crear su propio hardware, con la división Annapurna Labs de AWS, dedicada a diseñar chips para sus servidores. Pues bien, aquí te vamos a presentar estos chips llamados Graviton.

De hecho, hay que decir que los chips Graviton para servidores son los chips basados en Arm con el mayor volumen en servidores de la actualidad, lo que es muy indicativo. Así que vamos a analizar qué son exactamente.

Arm gana terreno en el sector de servidores y HPC

La elección de Annapurna Labs por la ISA Arm no es casualidad. Ya existía un floreciente mercado de servidores de pequeño tamaño y bajo consumo basados en Arm, aunque no podían competir con los procesadores más potentes.

En cambio, esto ha cambiado en los últimos años, cuando han irrumpido chips Arm muy potentes para servidores y HPC. Por ejemplo, como los Altra de Ampere Computing, los ThunderX de Marvell Technologies, e incluso los Fujitsu A64FX. Estos últimos han conseguido posicionarse en el número 1 de rendimiento de la lista Top 500 con la supercomputadora japonesa Fugaku para el RIKEN Lab.

A todos ellos también se les unió AWS con los Graviton, que fueron acogidos muy bien en el mercado, especialmente para aquellos que deseaban experimentar con Arm de alto rendimiento contratando los servicios de AWS, dada la falta de chips Arm de alto rendimiento para PCs. Ya que, a excepción de Qualcomm Snapdragon y Apple M-Series, no hay gran cosa por el momento…

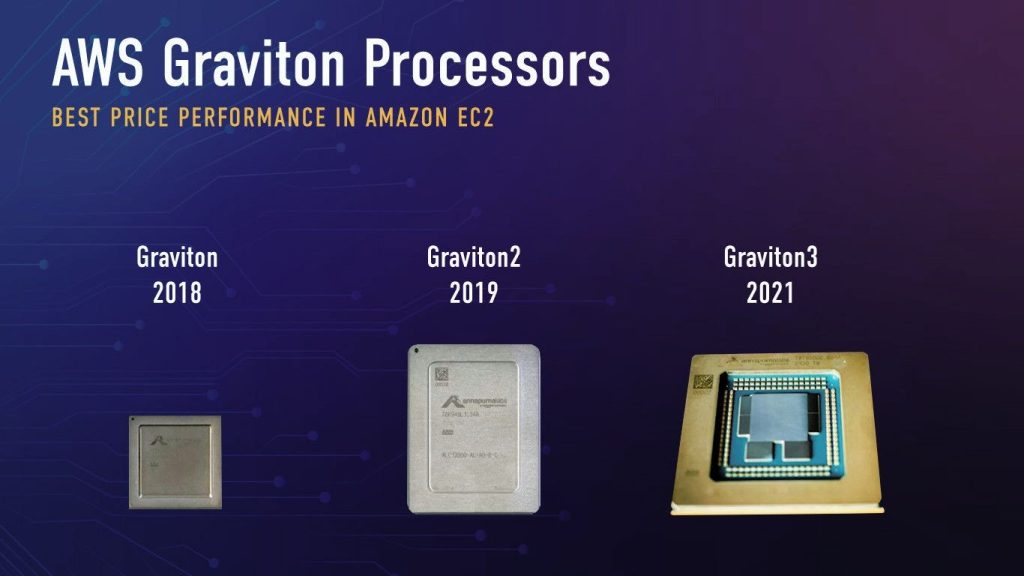

Dado el éxito de la CPU Graviton de 2018 (16 núcleos y 5.000 millones de transistores), después llegaría la segunda generación denominada Graviton 2 de 2019 (64 núcleos y 30.000 millones de transistores), y actualmente la tercera generación con el Graviton 3. Un chip Arm muy potente con 64 núcleos y 55.000 millones de transistores.

Además, hay que agregar que si quieres probar estos chips, puedes hacerlo en las instancias C7g del servicio EC2 que puedes contratar a través de los AWS de Amazon. Según AWS, gracias a estos chips consiguieron cifras del 40% de mejora en cuanto a precio/rendimiento sobre la misma generación de instancias M5, C5, y R5, además de una ventaja del 72% de reducción del consumo energético.

Hay que decir que AWS tiene un empeño más allá de explotar la interesante arquitectura Arm, por su relación rendimiento/vatio, y es que también pueden conseguir servidores más baratos que si compran CPUs a otros como Intel, AMD, IBM, etc. Además, ofrecen otra oferta diferente a los Xeon o a los EPYC, es decir, para aquellos clientes que no quieren una nube x86.

Instancias de AWS

AWS tiene más de 475 tipos de instancias EC2 diferentes entre sus servicios, ya que podrás elegir una gama de CPUs diferentes, memoria, almacenamiento, redes, configuración de aceleradores, etc. Es cierto que las instancias basadas en Graviton son una parte pequeña por el momento, pero poco a poco van cobrando importancia.

Estas instancias pueden ejecutar diferentes sistemas operativos Linux, como RHEL, Ubuntu, SUSE, etc., y cada vez más empresas están interesadas en desarrollar para esta plataforma.

En cuanto a las instancias que usan estos chips, tenemos:

- Graviton 1: EC2 A1

- Graviton 2: EC2 M6g, M6gd, C6g, C6gd, C5gn, R6g, R6gd, T4g, X2gd, G5g, Im4gn, Is4gen.

- Graviton 3: EC2 C7g, C7gn, HPC7g.

Como sabes, otras instancias de AWS también emplean procesadores AMD EPYC e Intel Xeon. Además, la competencia, como Microsoft Azure y Oracle OCI, que también ofrecen chips ARM, se basan en Ampere Altra.

Arquitectura Graviton

Como hemos dicho, los AWS Graviton diseñados por la división Annapurna Labs, se basan en la arquitectura ARM, son de 64-bit y tienen las siguientes características destacables:

- Graviton: es una CPU de 16 núcleos Cortex A72, con la ISA ARMv8-A y se incluyen las extensiones Neon, crc, y crypto. Usan un esquema de memoria NUMA y pueden trabajar a 2.3 Ghz. También se incluye en las instancias hardware de aceleración dedicado para coma flotante, SIMD, y para algoritmos AES, SHA-1, SHA-256, GCM y CRC-32.

- Graviton 2: es una CPU de 64 núcleos personalizados, a diferencia del Graviton 1. En este caso se usa la arquitectura Arm Neoverse-N1 para los núcleos. Esta basada en la ISA ARMv8.2-A, y se incluyen extensiones Neon (2×128-bit), LSE, FP16, RCPC, DOTPROD, CRYPTO. También emplean NUMA y pueden correr a 2.5 Ghz.

- Graviton 3: una CPU basada en 64 núcleos Arm Neoverse-V1, con una ISA ARMv8.4-A, y con extensiones Neon (4×128-bit), LSE, SVE (2×256-bit), RNG, BF16, INT8, CRYPTO. Usan organización NUMA y trabajan a 2.6 Ghz. Comparado con Graviton 2, la tercera generación es un 25% más potente, hasta dos veces más poderosa en coma flotante, 2 veces más rápida en cargas de trabajo de cifrado, y hasta 3 veces más rápida en cargas de Machine Learning, así como un 60% más eficientes y con un 50% más de ancho de banda de memoria.

En el siguiente apartado desgranamos de forma más detallada el nuevo Graviton 3…

Gravitón3 en profundidad

Mientras el Graviton 1 y 2 eran chips monolíticos, el Graviton 3 se basaba en un diseño chiplet. Está diseñado por Annapurna Labs, una división de AWS de Amazon. Y se fabrican en TSMC, con un nodo de 7 nm. Además, la primera vez que apareció este chip fue en mayo de 2022, y fue la primera CPU ARM para servidores en introducir las instrucciones SVE.

- Diseñador: Annapurna Labs

- Nodo de fabricación: 7 nm de TSMC

- Recuento de transistores: 55.000.000.000

- Empaquetado: MCM o chiplets

- Familia: Alpine

- ISA: ARM (ARMv8.4-A) + Extensiones Neon (4×128-bit), LSE, SVE (2×256-bit), RNG, BF16, INT8, CRYPTO.

- Microarquitectura: Arm Neoverse-V1 modificada

- Número de núcleos: 64

- Frecuencia de reloj: 2.6 Ghz

Microarquitectura

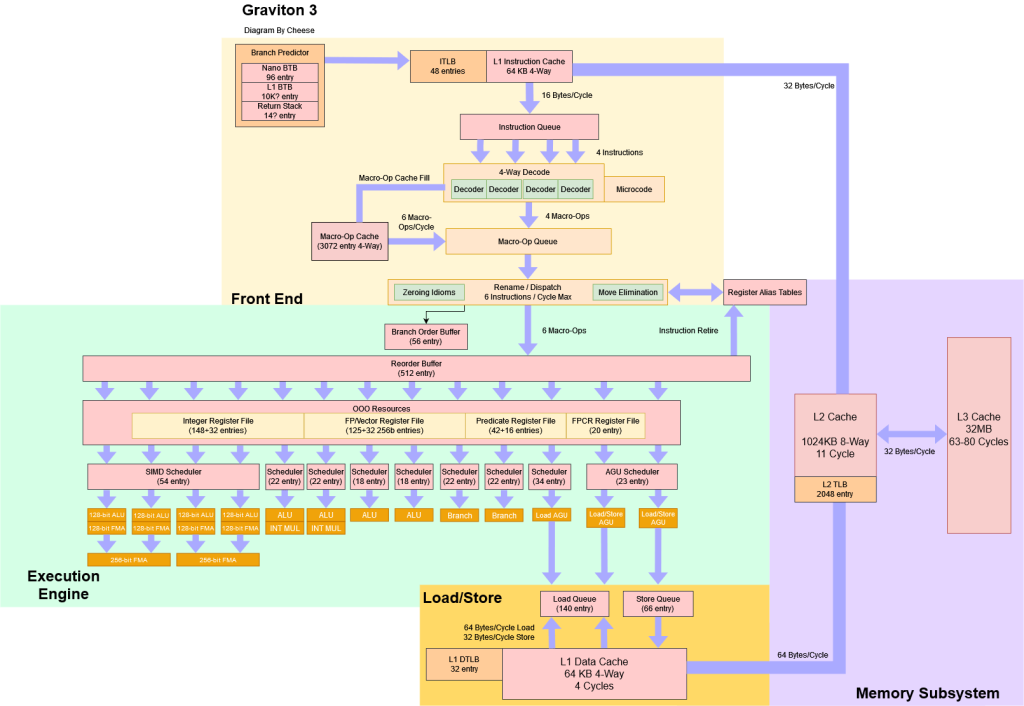

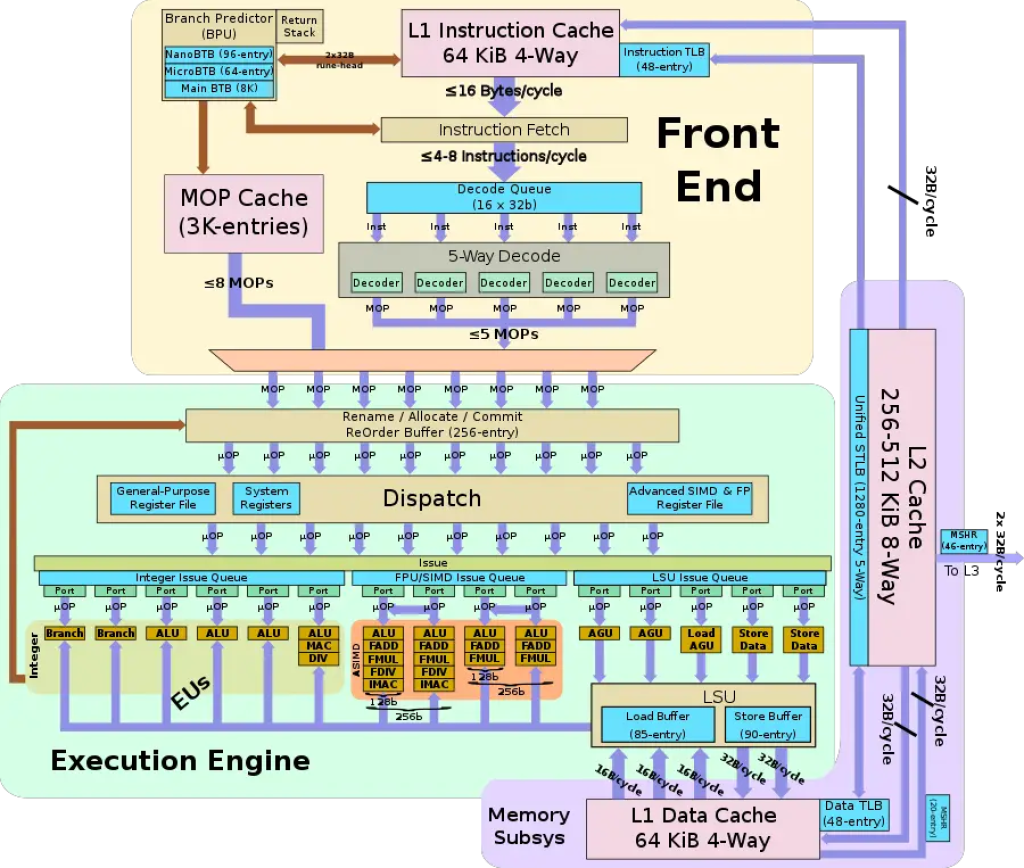

Como vemos, la microarquitectura del Graviton 3 no es exáctamente igual que la del Arm Neoverse-V1, como se puede ver en el siguiente diagrama:

Predictor

Entre algunas cosas que se pueden apreciar en estos diagramas está la mejora que ha hecho ARM en la V1 respecto a la N1 en el predictor de ramas, tanto en precisión como en velocidad, lo que hace que el predictor acierte en más casos y acelere el proceso, sin necesidad de limpiar el cauce de la pipeline en caso de fallo con tanta frecuencia, ya que eso penaliza el númeor de ciclos de reloj desperdiciados. Parece que Graviton 3 ha apostado por un diseño más parecido al del Intel Ice Lake SP. Comparado con el AMD Zen 3 (Milan), es algo menos capaz (usa solo un nivel, y no dos, aunque puede reconocer patrones muy largos, con hasta 512 ramas), pero más rápido.

Graviton 3 también tiene una configuración de BTB (Branch Target Buffer) muy rápida, permitiendo manejar ramas tomadas con muy poca penalización en los ciclos de reloj. De hecho, se permite que se manejen dos ramas por ciclo de reloj, una capacidad que hasta ahora solo habíamos visto en la microarquitectura Intel Golden Cove y Rocket Lake. Aunque hay que destacar que en en Intel no es tan rápida.

También existe un BTB principal muy grande, de unos 4K entradas y un L2 BTB que podría tener hasta 10K entradas, según se rumorea. Gracias a esto, se puede tener una mayor capacidad de manejar las ramas o bifurcaciones sin introducir tantas «burbujas» en la pipeline.

Front-End

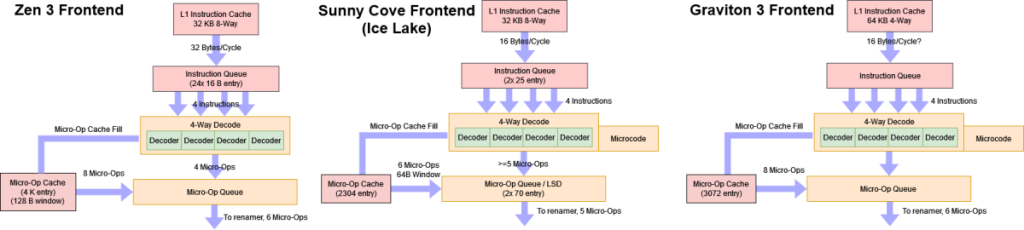

También me gustaría señalar que han usado un Front-End bastante parecido a las microarquitecturas Intel y AMD, como se puede apreciar en la siguiente imagen:

Si comparamos la Neoverse N1 con la Neoverse V1 en la que se basa Graviton 3, vemos que los decodificadores de la V1 son mucho mejores para procesar instrucciones. Y se ha usado un método similar a los x86. Además, se ha incluido una caché de microoperaciones. Todo esto hace que el Graviton 3 muestre unas capacidades de recuperación de instrucciones o ancho de banda de instrucciones similares al AMD Zen 3, con hasta 6 IPC.

Por otro lado, vemos cómo Graviton 3 ha creado colas de recuperación más profundas para obtener instrucciones de una forma más agresiva, y la caché L3 del Graviton 3 consigue una latencia más baja en comparación con Ampere Altra y Graviton 2. No obstante, aún no es comparable a los diseños de Intel y AMD, pero Arm está progresando en ese sentido.

Renombre de registros

El renombre de registros es otra práctica común en las modernas microarquitecturas, y el Graviton 3 parece muy similar a los núcleos Zen 3 en este sentido. Arm ha realizado mejoras en el V1 respecto al N1, aunque aún está por detrás de AMD e Intel en algunos sentidos, ya que tanto una como otra empresa introdujeron mejoras importantes en este sentido, para agiliar los procesos.

| Graviton 3 | Ampere Altra (Neoverse N1) | Intel Ice Lake (Sunny Cove) | AMD Zen 3 | |

| MOV independiente r,r | 3.81 | 2.86 | 4.77 | 5.72 |

| MOV dependiente r,r | 1.36 | 1.38 | 4.76 | 5.7 |

| XOR/EOR r,r | 1.00 | 1.00 | 3.81 | 5.72 |

| MOV r, 0 | 5.71 | 3.63 | 3.82 | 3.81 |

| SUB r, r | 1.00 | 1.00 | 3.81 | 5.7 |

Graviton 3 no puede hacer lo mismo que sus competidores de Intel y AMD. Claramente el rendimiento parece estar limitado por el número de puertos ALU. Al igual que Neoverse N1, Graviton 3 a veces puede romper las dependencias entre MOV de registro a registro, pero tiene capacidades muy limitadas en esa área.

Sin embargo, hay que decir que Graviton 3 tiene una ventaja sobre Ice Lake en este sentido, ya que el renombrador de Intel puede romper las dependencias cuando se detectan modismos de cero, pero no puede eliminarlos. Por tanto, Graviton 3 es más parecido a Zen 3 en este sentido.

OoOE

Por supuesto, como la mayoría de CPUs de alto rendimiento, Graviton 3 usa ejecución fuera de orden o OoOE (Out-of-order Execution). En este sentido, parece que el tamaño del ROB (Reorder Buffer) o buffer de reordenamiento se ha hecho corresponder con la cantidad de microoperaciones que puede traer el motor de ejecución del Front-End de esta CPU. Por tanto, podría estar en 512 entradas, según algunas pruebas, ya que Amazon no ha dado detalle de esto. No obstante, parece que la ventana de reordenamiento es superior a los diseños de Intel y AMD.

Registros y cola de carga

raviton 3 también parece tener un registro de archivo bastante grande, como es frecuente en los diseños RISC. Concretamente parece tener 125 registros vectoriales de 256-bit de ancho cada uno, según las pruebas de ingeniería inversa. De esta forma puede trabajar con las longitudes de NEON (128-bit) y de SVE (256-bit).

También se han observado algunas cosas extrañas en el archivo de registro del Graviton 3, ya que tiene un tamaño más apropiado para un ROB de 256 entradas que para uno de 512 entradas. También destaca la capacidad de cola de carga del Graviton 3, más o menos en la línea de AMD Zen 2 y Zen 3.

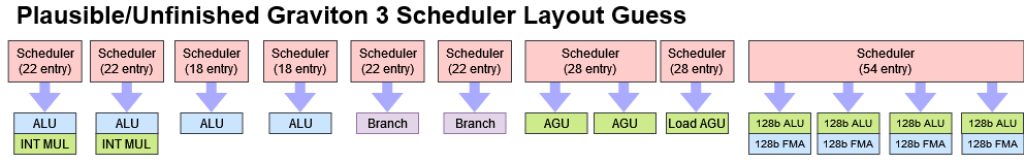

Planificador (Scheduler)

Otro componente importante de la CPU es el scheduler o planificador. Aunque desde Annapurna Labs no se han dado detalles, parece que las pruebas han destapado algunos secretos.

| Entradas del planificador del Graviton 3 | ||

| Suma de enteros | 81 | |

| Multiplicación de enteros | 44 | |

| Rama (no tomada) | 43 | |

| Multiplicación y bifurcación de enteros alternos | 82 | |

| Sumador escalar FP | 54 | |

| Multiplicar escalar FP | 54 | |

| Suma y multiplicación FP alternas | 54 | |

| Suma SVE FP de 256 bits | 56 | |

| Convertir entero a coma flotante (FP) | 22 | |

| Store, Dependencia de dirección | ¿28? | |

| Store, Dependencia de datos | ¿28? | |

| Load | ¿54? | |

| Load/Store alternativo, dependencia de dirección | ¿54? |

Graviton 3 tiene muchas entradas del planificador para realizar operaciones comunes, lo que supone un gran salto con respecto a Neoverse N1. A primera vista, parece más o menos comparable con Zen 3 y Ice Lake, al menos en términos de entradas del programador disponibles para operaciones comunes.

Unidades funcionales de ejecución (Back-End)

Por otro lado, y no menos importante, están las unidades de ejecución del Graviton 3, es decir, las unidades ALU y FPU, entre otras, donde se realizan los cálculos sobre los datos que indican las instrucciones del software procesado. Al ser un núcleod e alto rendimiento, se espera un puntos destacables en este sentido.

En el Graviton 3 tenemos cuatro ALU (Arithmetic Logic Unit) para enteros, en comparación con las 3 del Neoverse N1. También se aprecian 3 canalizaciones de memoria frente a las 2 de Neoverse N1.

En cuanto al coma flotante y la ejecución vectorial, también vemos cambios en los recursos destinados para ello. Por un lado tenemos unidades para realizar las sumas y multiplicaciones en coma flotante de las instrucciones SVE de 256-bit, que pueden ejecutarse en tan solo 2 ciclos de reloj. También hay grandes mejoras en la FPU par aprocesar operaciones de coma flotante con respecto al Neoverse N1, y se ha bajado la latencia.

Las mejoras le han servido al Graviton para ponerse por delante en agiliad con respecto a Intel y AMD en este sentido. Por ejemplo, podemos ver que necesita menos ciclos de reloj para completar estas tareas:

| Operación | Graviton 3 | Neoverse N1 | AMD Zen 3 | Intel Ice Lake SP (Sunny Cove) |

| Suma FP | 2 | 2 | 3 | 4 |

| Multiplicación FP | 3 | 3 | 3 | 4 |

| FP Fusionado Multiplicar+Suma (FMA) | 4 | 4 | 5 | 4 |

| Suma de enteros vectoriales | 2 | 2 | 1 | 1 |

| Multiplicación de enteros vectoriales | 4 | 5 | 3 | 10 |

No es de extrañar que Intel se tome tantos ciclos en las vectoriales, ya que ten en cuenta que usa AVX-512, que son vectores de 512-bit de longitud, por lo que son complejos de mover. En cambio, tanto en el caso de AMD como de Graviton 3, las operaciones más largas son de 256-bit.

Caché y acceso a memoria

Por supuesto, además de la caché L3 de 32 MB y la L2 de 1 MB, también se ha dotado a estos núcleos de una L1 de datos de 64 KB y una L1 de instrucciones de 64 KB. En el caso de la L2 y L3 son unificadas, y mientras la L1 y L2 son para cada núcleo, la L3 está compartida entre todos los núcleos.

Por otro lado, hay que decir que tanto Graviton 3 como Intel Ice Lake usan enfoques de caché L3 unificada similares, mientras que AMD adopta un enfoque diferente, dividiendo la L3 en bloques para compartir solo entre los núcleos de cada cluster, lo que hace que la L3 sea más rápida.

Pero más allá de la capacidad, que no es lo más importante, hay que ver la latencia de acceso a esta memoria. En este caso, tenemos que Graviton 3 puede acceder a la L1D en 4 ciclos de reloj de penalización. Siendo superior en la L2 y aún más para la L3, que es la que más penalización tiene, aunque afortunadamente es mejor que la horrible latencia de L3 en los Ampere Altra.

En cuanto al acceso a la memoria principal, a la RAM, el Graviton 3 tiene peores cifras que su antecesor y que el Altra, esto es probablemente a que usa DDR5, que tiene peores latencias que la DDR4. Además, Graviton también ha colocado controladores de memoria en chips IO separados dentro del empaquetado, lo que podría perjudicar también a esta latencia.

Ten en cuenta que Intel usa los controladores de memoria en un chip monolítico, mejorando la latencia. En cambio, el diseño chiplets de AMD es más parecido a Graviton 3, aunque en el caso del Graviton 3 el acceso a memoria es 10 ns más lenta que en el caso de AMD.

Soporte SVE

Para finalizar, vamos a comentar sobre el soporte de SVE en el Graviton 3, ya que es la primera CPU de servidor basada en ARM que incluye estas extensiones de instrucciones de longitud 256-bit (2×256). Es cierto que el Fujitsu A64FX incluyó SVE primero (concretamente 1×512), pero era un procesador especialmente diseñado para supercomputación, y no para servidores.

No obstante, hay que decir que la adopción de SVE por parte de los compiladores y el software es muy limitada, por lo que se tardará un tiempo en saber si realmente es una ventaja o no, de forma similar a cuando apareció AVX-512 en los Intel.

SVE es compatible con compiladores como GNU GCC, así como con LLVM y Clang. Arm también ha creado un derivado de LLVM propio que también las admite. Con ellos se puede compilar software que aproveche estas instrucciones vectoriales.

Scalable Vector Extension (SVE), es una extensión opcional de la arquitectura ARMv8, para mejorar las cargas de trabajo científicas. Estas instrucciones, a diferencia de las fijas que usan Intel, AMD y otros, permiten implementar longitudes de vector variables desde los 128-bit hasta los 2048-bit.

Ahora ya tienes una visión más amplia de este gran desconocido, y es que no todo es Intel y AMD, hay mucho más allá de eso…