Actualizado a: 19 de diciembre de 2023

El estándar PCIe 6.0 ha emergido como una innovadora y potente tecnología para la interconexión de componentes de alto rendimiento, como serán las futuras tarjetas gráficas y también las unidades SSD, entre otras tarjetas de expansión. Desde su introducción, PCIe ha experimentado varias revisiones que han mejorado significativamente la velocidad de transferencia de datos entre diversos dispositivos, y esta actualización de 2022 promete mucho…

¿Qué es PCIe?

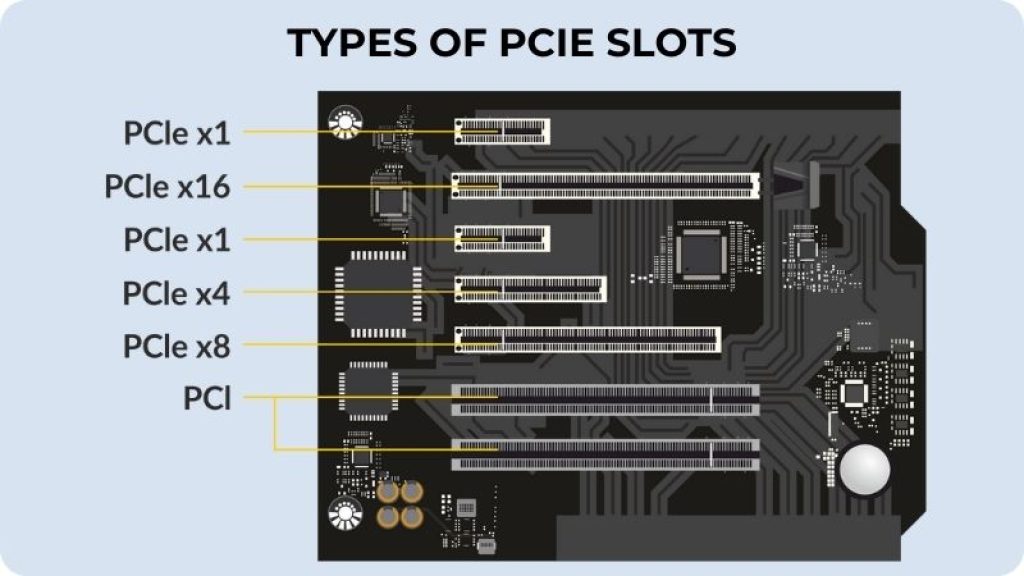

PCIe o PCI Express es una mejora del PCI (Peripheral Component Interconnect) anterior que se usó durante mucho tiempo para tarjetas de expansión, aunque para tarjetas gráficas se empleaba el conocido como AGP (Accelerated Graphic Port), ya que permitía un mayor ancho de banda y velocidad para la GPU. Sin embargo, con la aparición de PCIe, el gran rendimiento de esta interfaz ha hecho que también reemplazo al propio AGP x8.

No hay que confundir PCI Express con PCIx, ya que PCIx se refiere a PCI eXtended.

PCIe es una interfaz de interconexión desarrollada inicialmente por PCI-SIG, un consorcio de grandes empresas del sector que se ponen de acuerdo para marcar el rumbo de este estándar a nivel técnico y promoverlo. Entre los integrantes de PCI-SIG tenemos ejemplos como Acer, ADATA, Amazon, Ampere Computing, Analog Devices, AMD, Apple, ASUS, AverMedia, BAE System, Broadcom, ARM, IBM, Intel, Synopsys, NVIDIA, Qualcomm y un larguísimo etc.

La primera vez que apareció esta interfaz fue en 2003, y poco a poco fue sustituyendo a AGP y PCI, hasta que se ha transformado en una interfaz casi omnipresente en nuestros días. Sin embargo, a lo largo de la historia ha ido evolucionando mucho, desde la primera versión PCIe 1.0 hasta la PCIe 6.0. Pasando así desde los 2.5 GT/s y 250 MB/s iniciales por cada carril de datos, hasta duplicar eso en cada generación hasta nuestros días.

Especificaciones técnicas del PCIe 6.0

| Velocidad de transferencia de datos | 64 GT/s y 7.56 GB/s por cada carril |

|---|---|

| Formato de codificación | PAM-4 con FEC (Forward Error Correction) para la corrección de errores en la transferencia y con codificación por unidad de control de flujo (FLIT o Flow Control Unit) |

| Alcance del canal | Provisión de SNR reducida en 9 dB |

| Retrocompatibilidad | Sí, compatible con las anteriores versiones |

| Tasa de error de bits | 0.000001 |

| Tipo de bus | Full-Duplex (ambos sentidos) |

Mientras que la quinta generación, o PCIe 5.0 llegaba a los 32 GT/s, con 3.94 GB/s por cada carril y con hasta 63 GB/s para x16 o 16 carriles, el nuevo estándar PCIe 6.0 puede duplicar esto, con 64 GT/s de velocidad de transferencia de datos, PCIe 6.0 x1 puede llegar a los 7.56 GB/s y PCIe 6.0 x16 hasta los 121 GB/s. Una velocidad brutal para las futuras generaciones de tarjetas gráficas y de unidades SSD NVMe.

Pero cuidado, ya que la versión PCIe 7.0, que ya se está empezando a «moldear» llegará con hasta 128 GT/s, 15.13 GB/s por cada carril, lo que dará lugar a 242 GB/s en un x16. No obstante, éste estándar no llegaría hasta 2025, por lo que aún hay que seguir explotando el PCIe 5.0 y el PCIe 6.0 en los productos actuales.

Retrocompatibilidad de PCIe 6.0

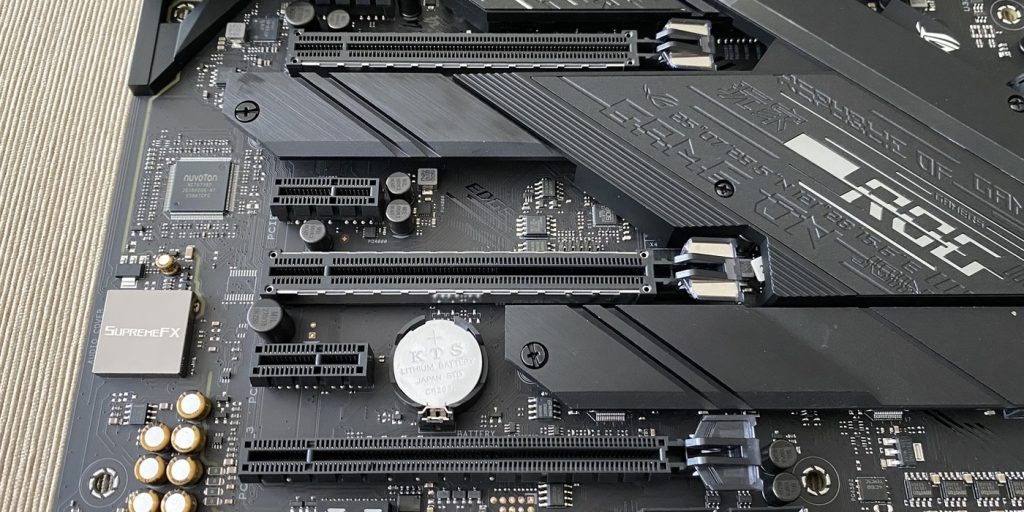

Como sabrás, la interfaz PCI Express ha mantenido la retrocompatibilidad a lo largo de sus versiones, lo que significa que es posible conectar tarjetas más antiguas en slots más recientes. Sin embargo, esta característica presenta un desafío, ya que para aumentar el ancho de banda, no se pueden agregar pines adicionales, lo que obliga a aumentar la velocidad de reloj.

En el caso de PCI Express 6.0, el aumento significativo de frecuencia de reloj ha llevado a ciertos problemas, ya que la estabilidad de la interfaz se ve comprometida a velocidades tan altas. Para transmitir datos a esas velocidades, la frecuencia de reloj de la interfaz debe llegar a 128 GHz, lo que afecta la integridad de la señal. Este desafío ha llevado a la implementación de medidas, comenzando por cambios en la codificación para hacer posible la transición a PCI Express 6.0 y en la inclusión de corrección de errores en este bus.

No obstante, hay que destacar algo, y es que retrocompatibilidad no significa compatibilidad hacia delante, es decir, si tienes una tarjeta de expansión PCIe 6.0, la puedes insertar en un slot o ranura PCIe 4.0, por poner un ejemplo, y funcionaría. Sin embargo, funcionará a la velocidad del PCIe 4.0, no a la del PCIe 6.0. Y lo contrario, si tienes una tarjeta de expansión PCIe 4.0 y la insertas en un bus PCIe 6.0, no va a funcionar a la velocidad del 6.0, sino del 4.0. Para aprovechar al máximo la velocidad, tanto el bus como la tarjeta tienen que ser de la misma especificación, solo entonces funcionarán a velocidad de la sexta generación…

Codificación PAM4

La transmisión de información en sistemas binarios se basa en el uso de voltajes distintos para representar los valores 1 y 0. En el caso del PCI Express 6.0, donde no es posible aumentar el ancho de banda sin distorsionar la señal ni agregar más pines para mantener la retrocompatibilidad, se ha adoptado la codificación PAM4 (Pulse Amplitude Modulation 4). Esta técnica utiliza cuatro valores de voltaje en lugar de dos, permitiendo codificar los valores 00, 01, 10 y 11 en cada pin. Aunque esta solución evita la necesidad de incrementar el ancho de banda y los pines, se sugiere que para el PCI Express 7.0 podrían ser necesarios enfoques no convencionales, como el uso de tecnologías fotónicas y interfaces ópticas.

Tecnologías FLIT y FEC

La adopción de PAM4 en la interfaz PCI Express 6.0 ha modificado la forma en que se envían los paquetes de datos, siendo incompatible con el sistema anterior, PAM2 o NRZ. La alta velocidad de PCI Express 6.0 puede causar inestabilidad y errores, lo que ha llevado a la implementación de un nuevo protocolo de corrección de errores llamado Forward Error Correction (FEC).

Este tipo de corrección de errores hacia adelante es una técnica utilizada en las transmisiones de datos para detectar y corregir errores que pueden ocurrir durante la transmisión, y así mejorar la fiabilidad de PCIe 6.0 a pesar de las velocidades alcanzadas. Pero, en lugar de solicitar la retransmisión de datos corruptos, como se hace en algunos protocolos de corrección de errores, FEC agrega información redundante al mensaje original antes de la transmisión. Esta información adicional permite al receptor detectar y corregir errores sin necesidad de solicitar una nueva transmisión.

Sin embargo, esto ha aumentado la latencia al pasar cada paquete de datos a través del sistema de corrección de errores. Para mitigar esto, se utiliza un tipo de paquete llamado FLIT, que tiene una latencia de 2 ns en una interfaz de 16 líneas, pero llega hasta 32 ns en una interfaz de una sola línea. El FEC opera con tamaños fijos, por lo que el FLIT tiene un tamaño de 256 bytes por envío. Cada paquete puede variar en tamaño de 0 a 4096 bytes y puede estar compuesto por varios FLITs.

Un Flit es una unidad atómica a nivel de enlace que forma un paquete. El primer flit, es el encabezado (header), contiene información sobre la ruta del paquete (especialmente la dirección de destino) y configura el comportamiento de enrutamiento a través de la interfaz para los flits siguientes. El último flit es el de cola (tail) y realiza algunas tareas de registro para finalizar la transferencia. para todos los flits subsiguientes asociados con el paquete.

La comprobación de redundancia cíclica (CRC) se ha incorporado al estándar PCI Express 6.0 para garantizar la integridad de los datos transmitidos mediante cálculos polinomiales realizados por unidades especializadas incluidas en la interfaz, lo que beneficia especialmente a los fabricantes de SSD al no requerir la adición de esta funcionalidad en sus unidades.

PCIe 6.0 incluye un nuevo modo de bajo consumo

PCIe 6.0 incorpora un nuevo estado de bajo consumo denominado L0P, que permite a la interfaz reducir su consumo de energía cuando el flujo de datos está por debajo de su capacidad máxima. Este modo ajusta la velocidad de reloj según las necesidades del dispositivo conectado en momentos en que los datos a transmitir son escasos.

Es importante destacar que este mecanismo está específicamente vinculado a las nuevas tecnologías introducidas en la sexta versión de PCIe, lo que implica que solo puede ser utilizado con dispositivos compatibles con esta generación. En otras palabras, el modo de bajo consumo L0P carece de retrocompatibilidad y solo funcionará con dispositivos que tengan compatibilidad nativa con PCIe 6.0.