Actualizado a: 19 de enero de 2024

Los transistores GAAFET, o transistores de efecto de campo de estructura envolvente, representan la próxima generación de tecnología de microprocesadores y otro tipo de chips avanzados. Estos transistores innovadores ofrecen una mayor eficiencia energética y un rendimiento mejorado en comparación con los transistores actuales, los FinFET. Como son el futuro más próximo, vamos a dedicar este artículo a conocer más acerca de ellos…

También te puede interesar:

Del transistor planar al FinFET

Desde que se desarrolló el transistor tipo MESA por parte de Jack Killby en la compañía Texas Instruments, hasta la llegada casi en paralelo del transistor planar de Fairchild Semiconductor y de la mano de Noyce, mucho han evolucionado estas estructuras.

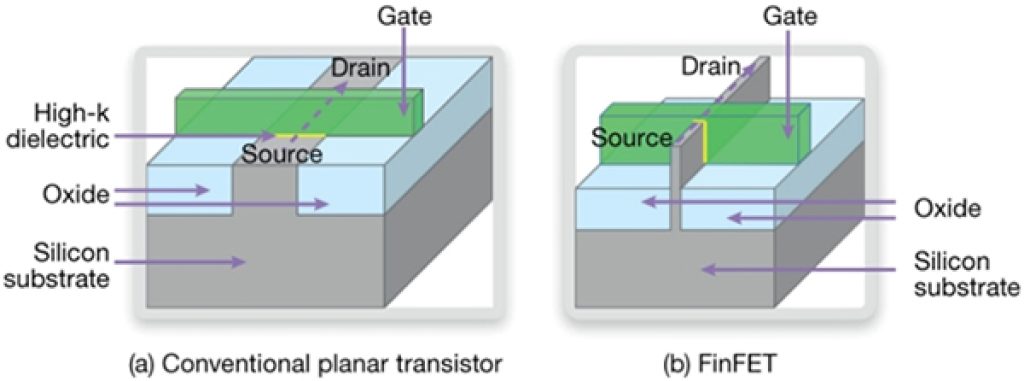

El transistor planar fue una tecnología ampliamente utilizada en la fabricación chips semiconductores con transistores tipo MOSFET (Metal-Oxide Semiconductor Field Effect Transistor). Esta estructura consiste en un canal y una puerta planos, que controlan el flujo de corriente a través del transistor. Sin embargo, a medida que los transistores se reducían de tamaño, se encontraron con desafíos como fugas de corriente y pérdida de control sobre el flujo de electrones.

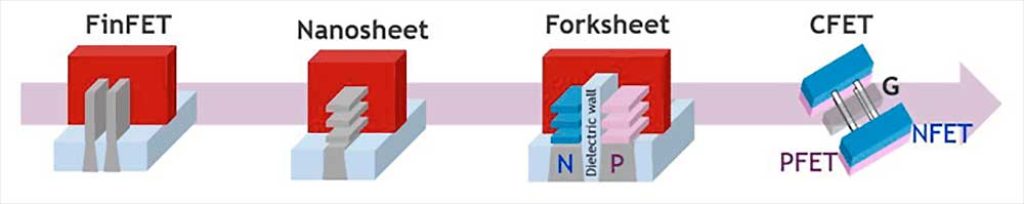

Para superar estas limitaciones, surgió una tecnología llamada FinFET (Transistor de Efecto de Campo de Aleta). El FinFET introduce una arquitectura tridimensional, donde el canal se levanta verticalmente, como una aleta, en lugar de ser plano. Esto permite un mayor control sobre el flujo de corriente, reduciendo las fugas y mejorando el rendimiento y la eficiencia energética.

El FinFET ha sido una evolución importante en el diseño de microprocesadores, ya que ha permitido el desarrollo de chips más pequeños y más potentes. Además, ha posibilitado el escalamiento continuo de los transistores, manteniendo el control adecuado a medida que se reducen aún más en tamaño.

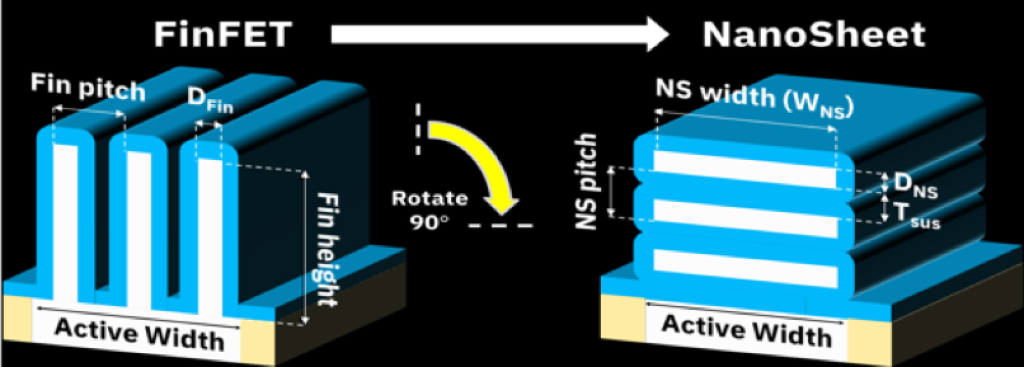

Sin embargo, incluso con los beneficios del FinFET, se están explorando y desarrollando nuevas tecnologías avanzadas próximas a los 5nm. Por ejemplo, se está investigando el uso de materiales más exóticos, como forksheet y nanosheets), así como estructuras completamente nuevas, como los transistores de efecto de campo de estructura envolvente (GAAFET). Estas tecnologías podrían brindar aún más mejoras en términos de eficiencia energética, rendimiento y escalabilidad.

¿Qué es un transistor GAAFET?

Un transistor GAAFET (Gate-All-Around Field-Effect Transistor) o SGT (Surrounding Gate Transistors) es un tipo de transistor que presenta una arquitectura tridimensional, donde la puerta envuelve completamente el canal del transistor. A diferencia de los transistores convencionales, que tienen una puerta plana en un solo lado, los transistores GAAFET/SGT tienen múltiples puertas apiladas alrededor del canal. Esto sigue el mismo principio que la construcción de rascacielos, pudiendo escalar hacia arriba para mayor densidad de integración, y mejorando las propiedades de los actuales FinFET en nodos de fabricación inferiores a los 5nm.

La estructura de múltiples puertas en el transistor GAAFET/SGT permite un mejor control del flujo de corriente y reduce las fugas de corriente, lo que resulta en una mayor eficiencia energética y un mejor rendimiento. Al envolver completamente el canal, las puertas ofrecen un mayor control sobre el flujo de electrones, lo que permite una mayor capacidad de encendido y apagado del transistor, lo que a su vez mejora la eficiencia y reduce la potencia consumida.

Este tipo de transistor se ha investigado y desarrollado como alternativa a los transistores FinFET en la búsqueda de tecnologías más avanzadas en la fabricación de microprocesadores y circuitos integrados de alto rendimiento, aunque algunos fabricantes se han topado con algunos problemas de yield en las obleas fabricadas con este tipo de transistores, por lo que necesita madurar. Una vez conseguido, se espera que los transistores GAAFET/SGT ofrezcan mejoras significativas en términos de rendimiento, eficiencia energética y escalabilidad, lo que los convierte en candidatos prometedores para futuras generaciones de dispositivos electrónicos de alta tecnología.

Nanohoja o Nanosheet GAA

Como expuso IBM en uno de los eventos para presentar las nuevas tecnologías venideras para la industria de los semiconductores, los GAAFET con nanoláminas o nanosheets apiladas horizontalmente están ganando aceptación en la industria como una solución para tecnologías de <5nm.

Estos dispositivos se construyen mediante capas alternas de silicio o germanio de silicio (SiGe), dispuestas en forma de pilares. La creación de la estructura inicial de Si/SiGe es relativamente sencilla y se asemeja al proceso de fabricación de aletas. Sin embargo, los pasos siguientes son específicos de los transistores de nanoláminas.

Una vez formadas las capas de SiGe, se crea una abertura en ellas para permitir la colocación de un espaciador interno entre la fuente y el drenaje, que posteriormente se deposita junto al pilar y el espacio destinado a la compuerta. Este espaciador determina el ancho de la puerta del transistor.

Luego, una vez que los espaciadores internos están en su lugar, se realiza un grabado selectivo para eliminar el material SiGe. Posteriormente, se utiliza la deposición por deposición atómica capa por capa (ALD) para depositar el dieléctrico y el metal de la compuerta entre las nanoláminas de silicio.

Sin embargo, tiene sus inconvenientes, como la mayor complejidad para su fabricación y el hecho de que sea importante minimizar la distorsión de la red y otros defectos, por lo que se busca mantener el contenido de germanio en las capas de SiGe lo más bajo posible. Sin embargo, se debe tener en cuenta que la selectividad del grabado aumenta con el contenido de germanio, y la erosión de las capas de silicio durante el grabado selectivo puede afectar el grosor del canal y, en última instancia, el voltaje umbral del transistor.

Nanocable o Nanowire GAA

En el ámbito de la investigación, diversos organismos están trabajando en el desarrollo de un transistor CFET de nanocables o nanowires. Por ejemplo, recientemente IBM presentó un FET de nanocables de silicio con una puerta completa, logrando un paso de nanocables de 30 nm y un paso de puerta escalado de 60 nm. Las dimensiones efectivas de los nanocables fueron de 12.8 nm. En el proceso de fabricación integral de puertas de IBM, se crean dos plataformas de aterrizaje sobre un sustrato, donde los nanocables se suspenden horizontalmente.

A continuación, se modelan puertas verticales sobre los nanocables suspendidos, formando múltiples puertas sobre una región común. Se crea un espaciador y posteriormente se cortan los nanocables de silicio fuera de la región de la puerta. Además, se cultiva una capa de silicio dopada epitaxialmente in situ a partir de las secciones expuestas de los nanocables en el borde del espaciador. El dispositivo se completa utilizando contactos de siliciuro a base de níquel autoalineables y conexiones de cobre.

Otras variantes

Existen otras variantes de transistores GAAFET. Por ejemplo, la Universidad Nacional de Singapur, Soitec y Leti presentaron un PFET de nanocables con una puerta de germanio (Ge). Este dispositivo, con un ancho de cable de 3.5 nm, se integró con un material de cambio de fase llamado Ge2Sb2Te5 (GST) como recubrimiento para aumentar la movilidad.

Además, la Universidad Nacional Cheng Kung desarrolló un MOSFET de nanocables de silicio apilados, que también se considera un tipo de FET de puerta, utilizando un sustrato Silicon On Insulator (SOI). Para permitir diseños de alto rendimiento y baja potencia, se empleó un esquema de dopaje flexible en el proceso. Mediante la utilización de epitaxia de superred de silicio/silicio-germanio y un proceso de dopaje in situ para los nanocables apilados, los investigadores lograron desarrollar un FET completo de puerta con cuatro nanocables apilados. La longitud de la puerta del dispositivo es de 10 nm, mientras que tanto el ancho como la altura del canal son de 10 nm, basándose en una longitud de escala electrostática de 3.3 nm.

En este contexto, los investigadores han implementado un enfoque diferente para el dopaje de los nanocables apilados, utilizando la epitaxia para implementar un canal dopado in situ en cada uno de ellos. Esto proporciona opciones flexibles para ajustar la tensión de umbral (Vt) en los MOSFET GAA (Gate-All-Around) apilados. Cabe destacar que el enfoque sin dopaje, aunque podría mejorar la movilidad y resolver el problema de la fluctuación aleatoria del dopante, no satisface las necesidades del diseño de múltiples Vt comúnmente utilizadas en aplicaciones de SoC (System-on-a-Chip). Por lo tanto, se requieren diferentes funciones de trabajo de puerta o materiales de puerta para diferentes valores de Vt, lo que agrega complejidad al proceso.

CFET: el futuro reemplazo de los GAA

El Complementary FET (CFET) es un dispositivo de compuerta integral más avanzado que ha sido diseñado para su uso en tecnologías de fabricación de 2,5 nm y más pequeñas. A diferencia de los transistores FET convencionales, que apilan múltiples cables tipo p o tipo n uno encima del otro, los CFET emplean una configuración donde se apilan cables nFET y pFET juntos. Esto significa que un CFET puede tener un nFET encima de un pFET, o incluso dos nFET encima de dos pFET.

El enfoque de apilamiento en los CFET elimina las limitaciones de separación entre cables tipo n y tipo p, lo que reduce la cantidad de área requerida en la celda activa. Esta «plegadura» de nFET y pFET ofrece beneficios significativos. Uno de los principales beneficios es la reducción del área necesaria. En términos de control electrostático, el CFET y un nanocable normal serían similares, ya que ambos son arquitecturas de puertas completas.

El CFET es un avance en la tecnología de transistores, que permite una mayor integración y eficiencia en tecnologías de fabricación más pequeñas. La capacidad de apilar dispositivos de tipo n y p juntos proporciona mejoras en el rendimiento y reduce el consumo de área, lo que lo convierte en una opción prometedora para futuros avances en la fabricación de dispositivos electrónicos de alta tecnología.

Aunque este es otro tema igualmente extenso que quizás veamos en otros artículos en el futuro…