Como bien sabes, uno de los mayores cuellos de botella actuales es la memoria RAM, ya que mientras las CPUs han aumentado a un ritmo muy acelerado, subiendo la velocidad y el rendimiento cada vez más, las memorias no han podido seguir el mismo ritmo y se han quedado algo rezagadas. Esto hace que actúen como un cuello de botella cuando la CPU tiene que acceder a ella, pese a la implementación del sistema de caché que resuelve en parte este problema. En cambio, se avecinan nuevos sistemas que podrían mejorar aún más este panorama, me refiero a la tecnología CXL que trataremos aquí.

Quizás también te puede interesar:

Memoria vs CPU: evolución

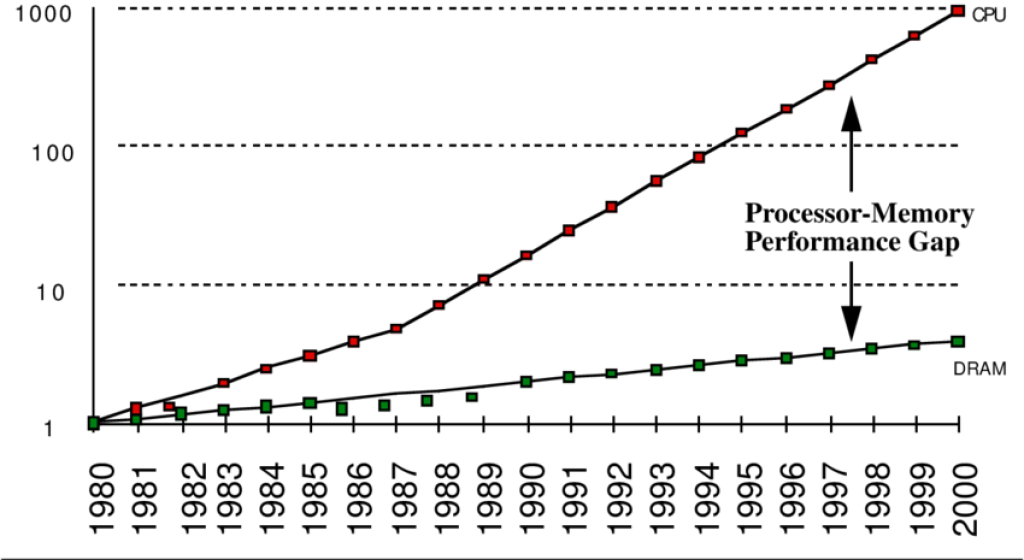

El ritmo de mejora de la velocidad de los microprocesadores supera con creces al de la memoria DRAM. Con el avance incansable de las unidades de procesamiento, el sector de la memoria se ha quedado algo rezagado, creando un cuello de botella importante como antes he comentado.

Como se aprecia en la gráfica, la CPU avanza a un ritmo anual de un 60%, mientras que la DRAM lo hace a un ritmo bastante inferior. Por tanto, cada vez existen más diferencias entre ambos componentes.

Solo hay que irse un poco atrás en el tiempo para ver, por ejemplo, el Intel Pentium III de 800 Mhz que iban equipados con módulos de memoria RAM SDRAM PC-100 de 100 Mhz, lo que significa que mientras un procesador podía realizar 800 millones de tareas por segundo, la memoria solo llegaba a los 100 millones de pasos por segundo.

Dicho de otro modo, cada vez que transcurren 8 ciclos de ese procesador se realizan 1 de la memoria. Eso quiere decir que en los accesos se podrían desperdiciar 7 ciclos. Y en la actualidad esto es superior, ya que los procesadores han seguido evolucionando a un ritmo superior que la DDR.

Esta desincronización en el ritmo de evolución y ese gap generado ha sido atajado a lo largo de la historia de varias formas:

- Primero se comenzaron a usar memorias intermedias entre las unidades de almacenamiento secundario y la CPU, ya que antes se usaba la unidad de almacenamiento como un punto de acceso directo para la CPU. Es así como surge la memoria RAM, que actúa como un buffer entre la CPU y los discos duros, que son aún más lentos que la RAM. De esa forma, la CPU no tiene que perder tantos ciclos.

- En cambio, dado que la memoria principal o RAM no ha avanzado tan rápidamente, se hizo precios la inclusión de una memoria intermedia entre la CPU y la RAM, conocida como caché. Primero implementadas en módulos en la placa base, para luego pasar a integrarse on-package en el mismo empaquetado de la CPU, hasta pasar a estar on-die o en el mismo chip que la CPU como en la actualidad.

- Luego vinieron los SSD, que trajeron velocidades de acceso superiores, pero aún así siguen siendo lentos como para eliminar las memorias intermedias…

¿Entonces? ¿Cuál sería la solución?

Como sabes, la memoria principal o RAM supone un factor de coste importante, y un consumo importante. Son dos problemas a atajar para que no sean un limitante de la CPU, especialmente en el sector HPC, donde esto supone un problema aún mayor.

Es por eso que la memoria CXL podría ser un paso adelante…

¿Qué es CXL?

CXL son las siglas de Compute Express Link, es decir, se trata de un estándar abierto para conexiones de la CPU a dispositivos E/S y de la CPU a la memoria, consiguiendo una alta velocidad y alta capacidad. Esta tecnología ha sido pensada especialmente para centros de datos, es decir, para equipos de alto rendimiento o HPC.

CXL se basa en una interfaz física y eléctrica serial e incluye un protocolo de E/S de bloque basado en la tecnología PCIe. Sin embargo, como puedes imaginar, esto también necesita de nuevos protocolos para mantener la coherencia en toda la jerarquía de memoria mientras se accede, y esto también ha sido implementado en esta nueva tecnología de la que te hablamos.

Aunque Intel fue el mayor impulsor de esta tecnología para sus Intel Xeon, el CXL Consortion está formado en la actualidad por multitud de miembros interesados como Meta, Dell, Cisco, Google, HPE, Huawei, Intel, Microsoft, AMD, NVIDIA, Samsung, ARM, Broadcom, IBM, Ericsson, Qualcomm, Marvell, Microchip Technology, SK Hynix, Western Digital, Rambus, Renesas, Seagate, Micron, Oracle, etc.

Hay que decir que en 2020 Gen-Z Consortium y CXL Consortium planearon que ambas tecnologías tuvieran interoperabilidad, apareciendo los primeros resultados en 2021. Es decir, unieron fuerzas para crear un desarrollo único del estándar industrial.

Más tarde, en 2022, las especificaciones y los activos de OpenCAPI de IBM también se habían transferido al CXL Consortium. Por tanto, ahora se incluyen en el estándar tecnologías como OpenCAPI de IBM, Gen-Z de HPE, CCIX de Xilinx (ahora AMD), InfiniBand/RoCE de Mellanox (ahora NVIDIA), Infinity Fabric de AMD, Omni-Path/QuickPath/UltraPath de Intel y también NVLink/NVSwitch de NVIDIA. Es decir, de los principales competidores del sector del alto rendimiento.

Versiones de CXL

En cuanto a las versiones que existen de CXL, tenemos:

CXL 1.x

Fue lanzada en 2019, basada en el protocolo de comunicación PCIe 5.0, consiguiendo velocidades muy elevadas. Esto permite a la CPU acceder a la memoria compartida entre dispositivos aceleradores con un protocolo coherente para la caché. No obstante, este sistema no era perfecto, y más tarde llegaría el CXL 1.1 con algunas mejoras, apareciendo justo en 2020.

CXL 2.0

En paralelo con la salida del 1.1, ese mismo año también llegaría la versión CXL 2.0 de esta especificación. En ella se agregaba retrocompatibilidad para la conmutación que permitía la conexión de varios dispositivos CXL 1.x y 2.0. Además, también también implementaba novedades para mejorar la integridad y el cifrado de datos para seguridad y mayor confiabilidad.

CXL 3.0

En 2022 llegaría CXL 3.0 basada en PCIe 6.0, con codificación PAM-4 y con el doble de ancho de banda que sus predecesores, lo que supone un enorme salto de rendimiento. Por supuesto, no solo se había mejorado el rendimiento, también se implementaron otras mejoras, como la coherencia mejorada con DMA punto a punto y uso compartido de memoria.

Protocolos CXL

Por supuesto, la tecnología CXL necesita de unos estándares para funcionar, concretamente se basa en 3 protocolos fundamentales denominados:

- CXL.io: basado en PCIe 5.0 con mejoras y con capacidad de configuración, inicialización y administración de enlaces, así como descubrimiento y enumeración de dispositivos, interrupciones, DMA y registro de acceso a E/S mediante Load/Store no coherentes.

- CXL.cache: este protocolo permiten que los dispositivos periféricos conectados al E/S puedan acceder de manera coherente a la memoria caché de la CPU con una interfaz de baja latencia.

- CXL.mem: sirve para que la CPU pueda acceder de forma coherente a la memoria del dispositivo en caché con comandos Load/Store para el almacenamiento volátil (RAM) y no volátiles o persistente (flash).

Ejemplos de implementaciones

Existen varias implementaciones de CXL en la actualidad que sirven como ejemplos, aunque no son demasiado populares para la mayoría de usuarios debido al sector al que van dirigidas. Algunos ejemplos son:

- Intel anunció en 2019 uno para sus FPGAs Agilex.

- Samsung anunciaría en 2021 un módulo de expansión basado en DDR5 de 128 GB y otra versión 512 GB basada en su propio controlador CXL patentado.

- En 2021 llegaría CXL 1.1 para los procesadores Intel Sapphire Rapids (Xeon). Lo mismo para los AMD EPYC basados en Zen 4 «Genoa» y «Bergamo».

Problemas que puede solventar CXL

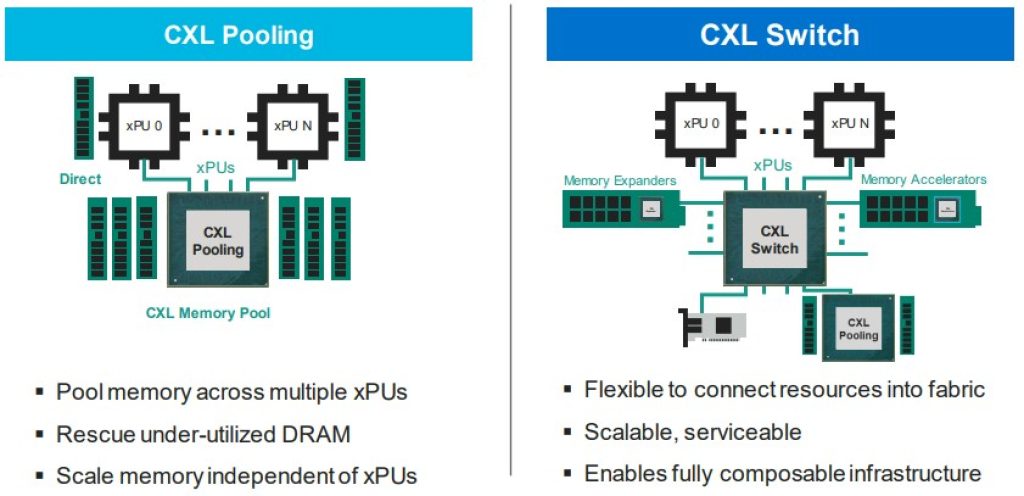

Actualmente, la memoria debe conectarse a una CPU, GPU, DPU, y otras unidades, mediante un controlador de memoria, ya sea la RAM o la VRAM, u otro tipo de memorias dedicadas o unificadas. Esto genera dos problemas básicos:

- Una memoria costosa que se termina infrautilizando.

- Problemas para escalar estos sistemas de alto rendimiento.

Por tanto, hay que buscar una solución para una memoria que pueda compartirse de forma más fácil y que sea más escalable. Por otro lado, también hay que tener en cuenta que el número de núcleos de la CPU está aumentando de forma muy rápida, y lo está haciendo más rápido de lo que lo está haciendo el ancho de banda, lo que genera otro problema de cuello de botella.

Con CXL, lo que se busca es precisamente tener sistemas de memoria convergente y que puedan superar estos inconvenientes. En el sector HPC, y se mira hacia CXL como una nueva esperanza, un nuevo estándar que seguir en un futuro para deshacerse de todos estos inconvenientes.

Es más, algunas empresas que han surgido en torno a CXL, podrán ayudar a crear factores de forma DIMM estándar, pero con controladores de expansión CXL, además de módulos de memoria más anchos y altos de factores de forma superiores a DIMM para albergar más capacidad en un solo slot. Aunque con la llegada del empaquetado 3D, quizás no sea tan necesario aumentar el tamaño de los módulos, con los inconvenientes que esto podría traer…

Como comenté antes, CXL también permitirá un ancho de banda mucho mayor para las comunicaciones entre la DRAM y la CPU, entre otras unidades, gracias al protocolo PCIe. Usando así carriles PCIe para agregar más ancho de banda cuando sea necesario para los módulos DIMM. Y mirando hacia el futuro, con la llegada de la DDR5, DDR6 y el PCIe 6.0, el futuro de CXL es prometedor…

El futuro es óptico

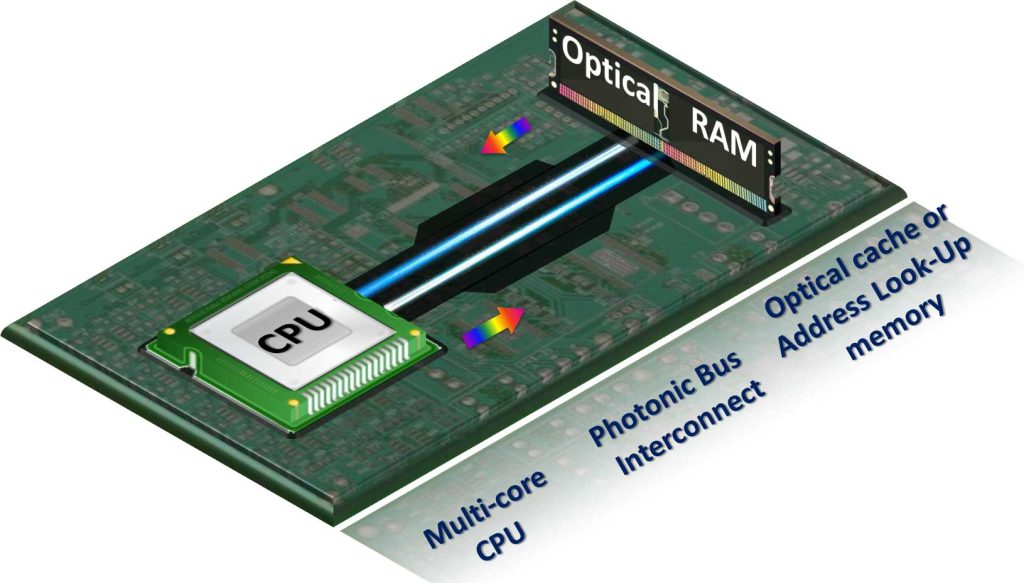

Como siempre suelo decir, el futuro es óptico. Y es que ya algunas empresas, como AMD, están patentando tecnologías muy interesantes para las interconexiones ópticas, es decir, basadas en señales de luz en vez de señales eléctricas, lo que conseguiría un mayor ancho de banda y velocidad del mismo modo que la fibra óptica ha conseguido en las redes.

Interconectar diferentes sistemas como la CPU y la memoria principal con un bus fotónico podría traer grandes ventajas de rendimiento para el futuro. Además, los chiplets y los empaquetados 3D también podrían interconectarse a otras unidades de procesamiento o chips de memoria como los HBM para mejorar el rendimiento y bajar las latencias.

Es decir, que no todo está dicho en el ámbito de la tecnología y pronto veremos surgir muchas novedades al respecto…

Los comentarios están cerrados.