Actualizado a: 19 de enero de 2024

Desde hace unos años se está hablando bastante del chiplet, o los chiplets, desde que AMD y su Zen hayan impuesto esta forma de crear los nuevos diseños mientras Intel mantenía la filosofía del chip monolítico. No obstante, el concepto de chiplet o MCM, no es tan reciente, y aquí vamos a ver todo lo que puede aportar y sus desventajas frente a los monolíticos…

¿Qué es un chiplet?

Un chiplet se refiere a un componente de circuito integrado, o chip, diseñado para colaborar con otros chips similares o idénticos. Esta estrategia implica reemplazar un solo chip de mayor tamaño o mayor complejidad por varios chips más pequeños.

La adopción de los chiplets surge debido al crecimiento constante en el tamaño de los chips y los problemas de yield o rendimiento de fabricación. Uno de los primeros ejemplos de su uso en procesadores comerciales fue con los AMD Zen, que la Dra. Lisa Su anunció en 2017.

A medida que las fundiciones mejoran los procesos de fabricación para crear componentes más pequeños, los chips de alto rendimiento se vuelven más complejos y grandes, lo que aumenta los costos de producción. En consecuencia, la fabricación de chips monolíticos de gran tamaño se vuelve económicamente menos viable. Por esta razón, se adoptan diseños basados en chiplets, que dividen un sistema complejo en unidades más pequeñas y simples.

Tomemos en cuenta que un chip mediano con un tamaño de matriz de aproximadamente 18 x 20 mm tiene una superficie de 360 mm². En un wafer de 300 mm de diámetro, se pueden fabricar alrededor de 150 chips de este tipo. Sin embargo, al dividir el diseño en cuatro chiplets de 9.5×10.5 mm, la superficie total es de aproximadamente 99 mm², lo que permite fabricar hasta 622 chips en una oblea.

Esta estrategia aumenta la tasa de producción efectiva, lo que significa más chips funcionales en comparación con el primer enfoque. En consecuencia, se logra reducir los costos de producción.

Es evidente que a medida que el tamaño de los chips disminuye, la producción es más eficiente, se desperdician menos chips y los costos pueden reducirse al fabricar más unidades en una sola oblea. Además, la Ley de Moore anticipa un aumento en la complejidad, y la aparición de los procesadores multinúcleo ha exacerbado aún más esta situación. La simple reducción en el tamaño de los nodos no es suficiente para mantener el tamaño de los chips, lo que resulta en un aumento en el costo.

Esta tendencia de los chiplets parece extenderse más allá de las CPUs y GPUs, impactando también en otros sectores como la industria automotriz y las memorias, transformándose en una tendencia dominante…

¿MCM vs chiplet? ¿es lo mismo?

Existe un enfoque de ensamblaje llamado MCM (Multi Chip Module) que ha sido utilizado durante muchos años. En este tipo de ensamblaje, varios chips son colocados sobre un sustrato y conectados entre sí, compartiendo pines o pads de conexión.

Los procesadores IBM POWER han utilizado el enfoque de empaquetado MCM, y recientemente, AMD también ha empleado esta técnica para sus procesadores más recientes. La distinción entre MCM y chiplets es importante:

- Mientras que MCM se refiere al método de empaquetado.

- Chiplets»se refiere a las unidades de chips en las que un sistema se divide. En otras palabras, cada circuito integrado es una parte funcional independiente del sistema completo y se llama chiplet. La colaboración de varios chiplets forma el conjunto completo.

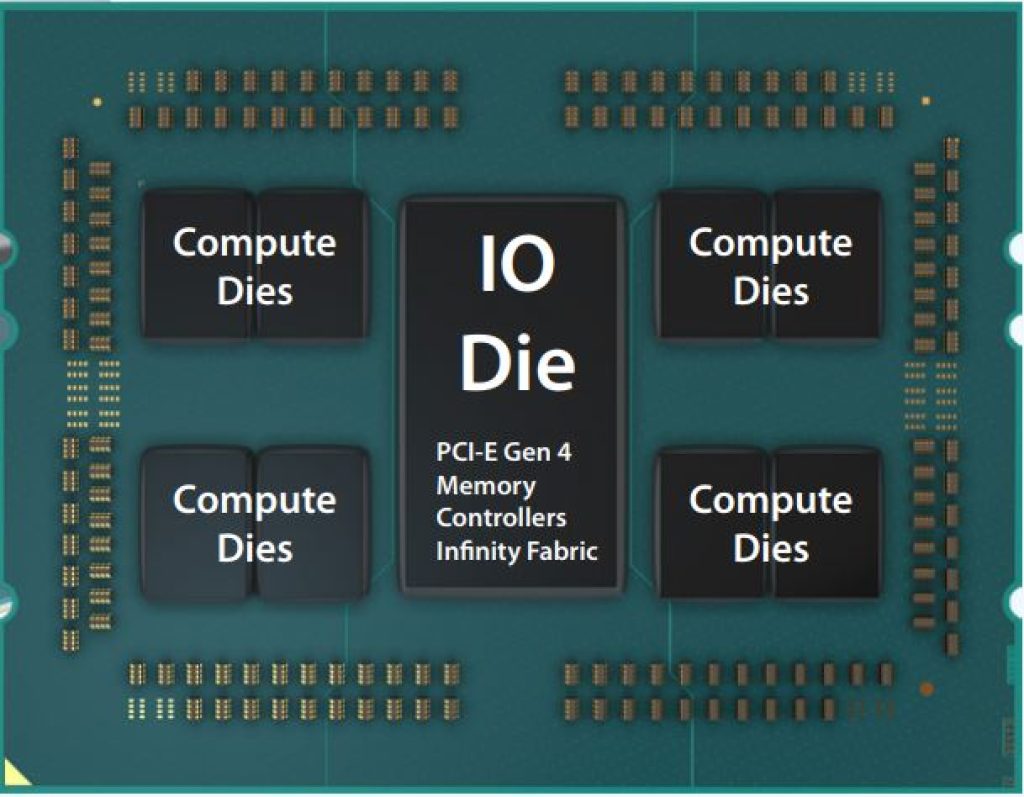

Por ejemplo, un AMD EPYC se divide en chiplets, pero utiliza un enfoque de empaquetado MCM. Intel también ha implementado este tipo de empaquetado en ciertos casos, como la integración de sus GPUs junto con las CPUs, en contraste con la estrategia de AMD en sus APUs. Ejemplos adicionales incluyen las GPUs AMD Radeon Instinct MI200 y las Intel Xe Ponte Vecchio.

Dentro de este tipo de empaquetado, se encuentran varias partes notables:

- Chiplets: son los componentes en los que el sistema ha sido dividido. Estos chiplets pueden representar diversos subsistemas, como unidades de memoria, procesamiento, comunicación, etc. Un ejemplo es el IBM POWER6, que se divide en núcleos de CPU y chips de caché L3 fuera del die.

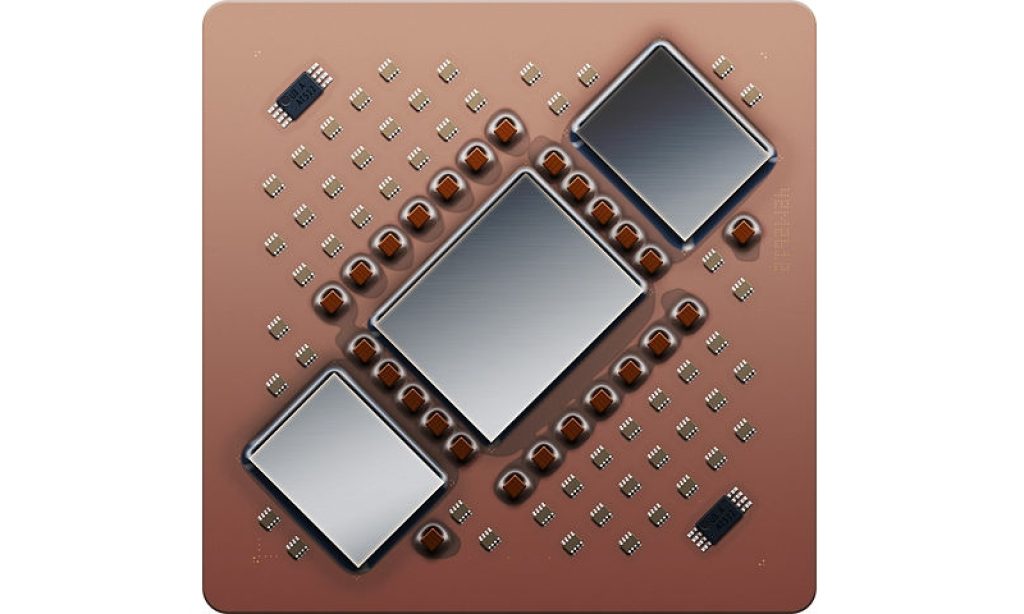

- Interposer: es el sustrato o PCB que facilita la interconexión entre los circuitos integrados o chiplets. Por lo general, está hecho de material orgánico. En el caso del IBM POWER6, esta área es de color marrón.

- Otros componentes: a menudo se observan componentes de montaje superficial en el interposer, como resistencias y condensadores. En el IBM POWER6, se pueden ver varios componentes SMD que rodean los chips.

Es destacable que el uso de chiplets y los nuevos métodos de empaquetado permitirán la integración de chips diversos, como diferentes tipos de procesadores, memorias y FPGAs programables que funcionan como aceleradores especializados. Esto da lugar a la idea de computación heterogénea.

Tecnologías complementarias importantes

Dentro del contexto del concepto chiplet, diversas tecnologías prometedoras se perfilan como complementos clave:

- HBM (High Bandwidth Memory): aunque HBM ha encontrado uso en diseños como las GPUs de AMD, su potencial se extiende también a las CPUs. Esta memoria de alto ancho de banda permite almacenar los recursos requeridos por las unidades de procesamiento en proximidad, reduciendo la latencia. Los chips HBM pueden ser incorporados en un formato chiplet (empaquetado 2.5D o MCM), junto con las unidades de procesamiento.

- Empaquetado 3D: para maximizar la capacidad de circuitos en un espacio dado, los productos basados en este empaquetado tridimensional están emergiendo. Esto implica apilar chips uno sobre otro, conectados a través de vías que atraviesan las matrices. Por ejemplo, la 3D V-Cache de AMD coloca una caché de memoria sobre una unidad de procesamiento, mejorando el rendimiento al reducir la penalización por fallos y minimizar la necesidad de acceder a niveles de memoria más lentos.

- DSA y FPGAs: la cercanía de la memoria HBM o la caché no es la única integración viable cerca de las unidades de procesamiento. FPGAs pueden ser incorporados, y en ellos, se pueden implementar DSAs (Domain Specific Accelerator), procesadores diseñados específicamente para acelerar tareas particulares. Ejemplos incluyen el Neural Engine de Apple en sus SoCs A-Series para IA. Esto no se limita a la IA, sino que puede aplicarse a una variedad de tareas.

- Computación Heterogénea: el empaquetado 3D y MCM son idóneos para la computación heterogénea. En lugar de confiar en que una unidad resuelva todo, este enfoque divide tareas eficientemente entre diferentes unidades. Por ejemplo, delegar cálculos de coma flotante a GPGPUs, sumas a DSPs, aprovechando las fortalezas específicas de cada unidad.

- Interconexiones Ópticas: mejorar la latencia y el ancho de banda en las interconexiones es vital, especialmente entre memoria y unidades de procesamiento. En este sentido, los enlaces ópticos, que transmiten pulsos de luz (más rápidos que señales eléctricas), están siendo explorados. Esto puede ser comparado a la diferencia entre una conexión ADSL y la fibra óptica en términos de velocidad.

- IA (Inteligencia Artificial): las redes neuronales y la IA juegan un rol importante. La implementación de redes neuronales en unidades de procesamiento puede elevar el rendimiento. Por ejemplo, en unidades de predicción de saltos, una red neuronal puede aprender patrones de comportamiento y optimizar la toma de decisiones. Esto resultaría en menos errores y menor vaciado de la pipeline debido a predicciones erróneas.

Es decir, el chiplet por si solo no es el futuro, sino que debe ir acompañado por otras tecnologías y desarrollos, para mejorar aún más la computación actual.

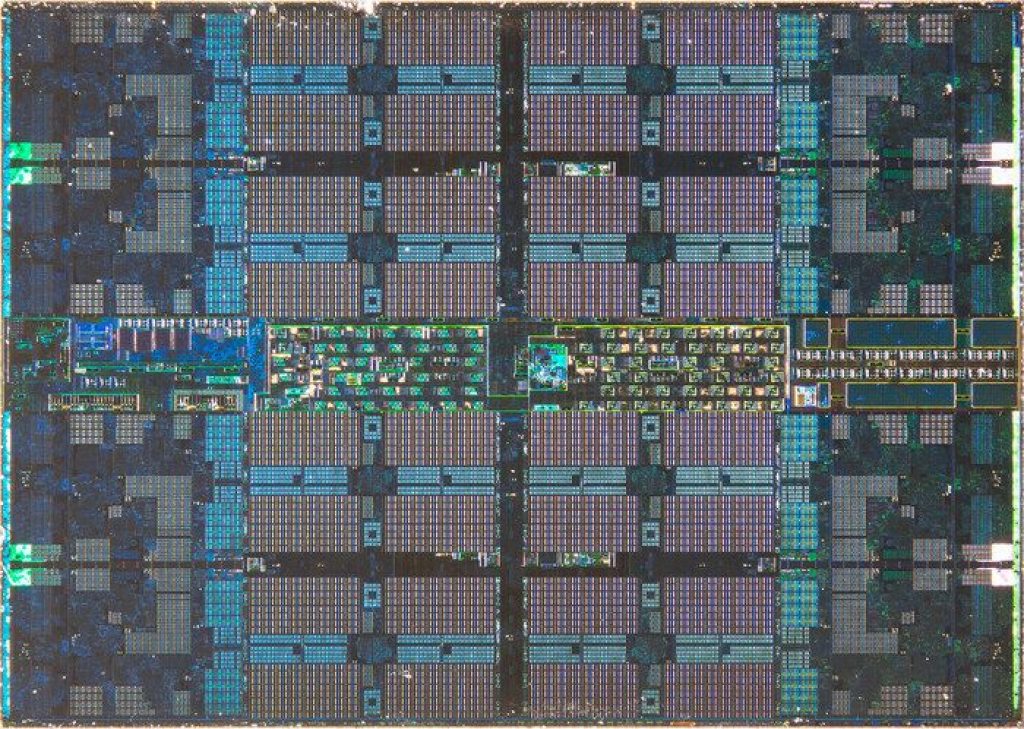

¿Qué es un chip monolítico?

Un chip monolítico es un tipo de circuito integrado en el que todos los componentes y circuitos electrónicos están construidos en una sola pieza de material semiconductor. En otras palabras, todos los elementos, como transistores, resistencias, condensadores e interconexiones, se fabrican en la misma superficie del chip utilizando procesos de fabricación semiconductor. En este enfoque, todas las partes del circuito están conectadas eléctricamente en la misma capa y no se utilizan componentes o piezas externas.

Este enfoque contrasta con la idea de chiplet, donde un sistema se construye a partir de varios chips más pequeños, cada uno de los cuales desempeña una función específica y luego se ensambla en un solo paquete. En un chip monolítico, en cambio, todas las funciones y circuitos se integran en una única pieza de silicio, lo que puede llevar a una mayor densidad de componentes y una integración más estrecha, pero también puede ser limitado por los desafíos de escalabilidad y complejidad de fabricación.

Chiplet vs chip monolítico: ventajas y desventajas

Ambos diseños tienen sus claras ventajas y desventajas, como es habitual en el mundo de la tecnología. Para saber cuál es mejor, vamos a desgranar cuáles son los pros y contras de cada una de ellas:

Chiplet

Aunque los diseños basados en MCM (Multi Chip Module) o chiplets presentan numerosas ventajas, también conllevan algunas limitaciones en comparación con los enfoques monolíticos, en los cuales todos los componentes se encuentran integrados en un solo chip. Entre las ventajas de los chiplets se encuentran:

- Reducción del tiempo de diseño.

- Disminución de los costos al mejorar el rendimiento del proceso de producción.

- Capacidad para utilizar mayor cantidad de memoria y más núcleos de procesamiento, lo que permite una mayor escalabilidad y modularidad.

- Posibilidad de emplear distintos nodos de fabricación, familias lógicas e incluso diferentes tipos de semiconductores en los diversos chiplets.

Sin embargo, también es importante considerar las desventajas asociadas con los chiplets, que incluyen:

- Mayor latencia en la comunicación entre unidades.

- Necesidad de interposers más complejos para facilitar la interconexión.

- Implementación de lógica adicional para la comunicación entre los distintos chiplets.

- La falla en la conexión de uno de los «die» puede resultar en la inoperabilidad de todo el dispositivo.

En la actualidad, se están desarrollando y lanzando al mercado soluciones destinadas a abordar estas desventajas inherentes a los chiplets, mientras se aprovechan las ventajas de este enfoque modular. Un ejemplo es la adopción de empaquetados 2.5D y 3D, que implican la superposición de chips para lograr latencias similares a las de un diseño monolítico, pero aún permitiendo la fabricación individual de cada chip apilado. Un ejemplo de esto es la tecnología 3D V-Cache, que apila chips de mayor capacidad de caché sobre las unidades de procesamiento.

Sin embargo, un desafío en este ámbito es la falta de estandarización, ya que los fabricantes están empleando métodos propios. Esto significa que si en el futuro se desea combinar chips de diferentes fabricantes en un mismo dispositivo, podrían surgir problemas de compatibilidad. Es probable que hayas escuchado términos como Intel Foveros, Intel EMIB, TSMC LSI, TMSC CoWoS, todos con sus particularidades y diferencias.

Chip monolítico

Los circuitos integrados monolíticos, al igual que los chiplets, presentan sus propias ventajas y desventajas, que se resumen de la siguiente manera. Entre las ventajas encontramos:

- Menor tamaño de empaquetado, lo que los hace especialmente adecuados para dispositivos móviles o sistemas embebidos con limitaciones de espacio.

- Empaquetado menos complejo y, por lo tanto, más económico.

- Mayor fiabilidad debido a la menor cantidad de componentes involucrados, lo que reduce las posibilidades de fallas en pistas conductoras y soldaduras, entre otros.

- Posible reducción en el consumo de energía.

- Transferencia de datos más rápida y con menor latencia entre las diferentes partes debido a su proximidad física y al hecho de que todas las unidades suelen operar a la misma frecuencia.

- Eliminación de la necesidad de lógica adicional para coordinar los diversos componentes, ya que todos están en una sola pieza.

Desgraciadamente, esta forma también tiene sus desventajas, como:

- Costes de fabricación más elevados que los chiplets debido a un rendimiento inferior en la producción.

- Concentración de una mayor potencia de disipación.

- Un fallo en un solo transistor o interconexión puede resultar en el fallo completo del circuito integrado.

- Menor flexibilidad y escalabilidad en comparación con los sistemas basados en chiplets.

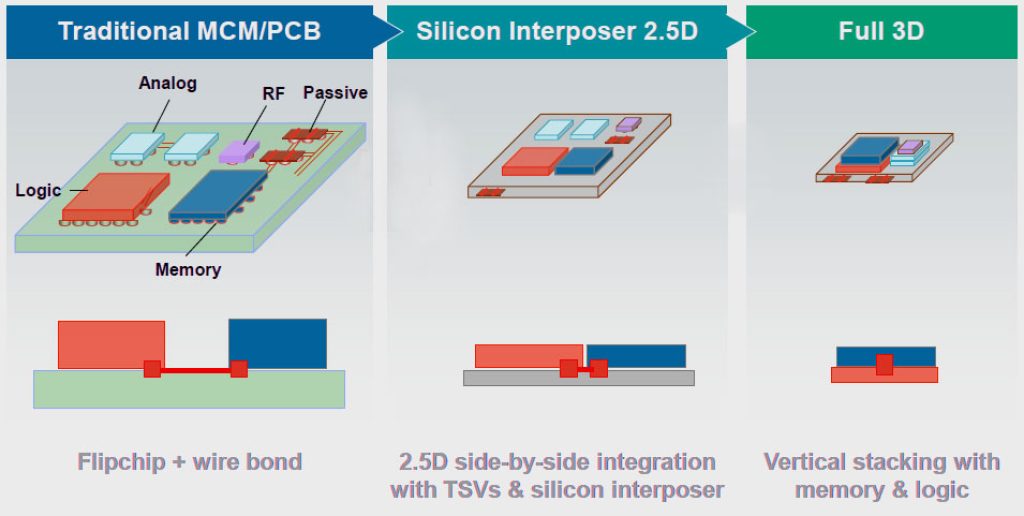

2.5D y 3D packaging: una solución con lo mejor de ambos mundos

En la configuración de empaquetados, los componentes se organizan en la placa de circuito y se conectan mediante diminutos cables. En todos los métodos de empaquetado en 3D, los chips dentro de un paquete se comunican a través de señales externas al chip, de manera similar a como estarían ubicados en paquetes separados en una placa de circuito convencional. En las CPUs 3D, las memorias HBM y otros chips de Intel, se utilizan pequeñas bobinas de cobre como interconexiones dentro del paquete, junto con el proceso de volteo del chip.

Una técnica llamada Hybrid Binding, o unión híbrida, apila y conecta los chips utilizando conexiones de cobre a cobre extremadamente pequeñas, lo que resulta en una mayor densidad y rendimiento en comparación con los esquemas de interconexión de chips apilados actuales. La unión híbrida de cobre, una tecnología relativamente nueva realizada en instalaciones de fabricación de semiconductores, representa una vanguardia en la capacidad de apilar chips, ofreciendo ventajas competitivas a los clientes de chips. La primera generación de chips que incorporan esta tecnología, conocida como hybrid bonding, marca el inicio de una nueva era competitiva en productos de chips basados en 3D y envases avanzados.

AMD ha sido el primer fabricante en introducir chips con unión híbrida de cobre, una tecnología avanzada para el apilamiento de chips que allana el camino para la próxima generación de dispositivos y empaquetados en 3D. Denominada hybrid bonding, esta tecnología proporciona nuevas posibilidades para los diseños de alta gama, abriendo la puerta a la próxima generación de diseños en 3D, matrices de RAM en 3D y envases aún más avanzados. La unión híbrida es una tecnología crucial tanto para unir obleas como para unir chips.

En este contexto, la tecnología de interconexión determina cómo se apilan y conectan las matrices en los paquetes. En un circuito electrónico tradicional en 2D, cada matriz se empaca individualmente. En los chips 3D, las matrices están apiladas mucho más cerca que en un circuito impreso tradicional.

Este enfoque requiere un diseño de chips que considere la disposición de las matrices y la utilización de maquinaria especializada para su alineación y unión. Cada matriz en una pila debe ser diseñada teniendo en cuenta el apilamiento, lo que representa un esfuerzo de diseño significativo. Las combinaciones de pilas de matrices pueden ser posibles en chips 3D, mientras que serían inviables en los chips 2D.

En lugar de acomodar chips separados en matrices interconectadas horizontalmente y contenidas en sus propios paquetes, las tecnologías más avanzadas apilan los chips en capas verticales en un pequeño encapsulado, formando el sistema completo. En la industria actual, se emplean técnicas de empaquetado sofisticadas para incorporar múltiples chips de alta gama y/o maduros en un solo envase, lo que se conoce como integración heterogénea.

Métodos de empaquetado multidimensional

En relación a las tecnologías disponibles en el mercado de empaquetado de semiconductores en 3D, hay diversas categorías, como los agujeros pasantes de silicio en 3D, los paquetes en 3D sobre otros paquetes, las bases de abanico en 3D, las interconexiones mediante enlaces de alambre en 3D, entre otras. Un enfoque para segmentar este mercado se basa en los tipos de interconexión utilizados, incluyendo la unión de cables, el flip-chip, el empaquetado a nivel de oblea (WLP) y la tecnología vía-silicio-vía (TSV).

Dentro de los ejemplos de empaquetado en 3D se encuentran el POP (Package-on-Package), en el cual se empacan matrices individuales que luego son apiladas y se forman las conexiones mediante procesos de wirebond o flip-chip. También se encuentra el empaquetado en 3D a nivel de oblea (3D WLP), que emplea capas de redistribución (RDL) y el proceso de bumping para establecer las interconexiones. Aunque se busca incrementar la densidad de empaquetado, muchos de estos dispositivos aún utilizan tecnologías más tradicionales como wire bonds y flip chips.

La demanda de chips con enfoques avanzados de empaquetado de semiconductores está impulsada principalmente por tamaños más reducidos y menor consumo energético. Una de las técnicas en esta área es el diseño de empaquetado tridimensional, que permite a los diseñadores de chips utilizar tecnologías más avanzadas en áreas críticas como las unidades de procesamiento, mientras que emplean tecnologías más antiguas en áreas menos sensibles a la velocidad, lo que resulta en ahorro de costos. La tendencia actual en la fabricación de chips se enfoca en apilar chips más pequeños en una capa básica de silicio, mezclando diversas tecnologías en lugar de construir un solo chip grande.

Intel ha compartido información preliminar sobre su tecnología EMIB/Foveros, un enfoque de empaquetado en 3D que debutará en productos el próximo año y permitirá apilar chips lógicos complejos y diversos uno sobre otro el año siguiente. Para apoyar esta innovación, Applied Materials y el IME han establecido un laboratorio de empaquetado de chips en 3D de última generación en Singapur. Además, la principal fundición de semiconductores de Taiwán planea una instalación en Estados Unidos para la producción de obleas. Otros como Samsung o TSMC también tienen sus propias tecnologías, como es el caso de CoWoS/3D Fabric de TSMC…

La capacidad de empaquetar más transistores en los SoC y alcanzar el rendimiento necesario para la competencia es un motivo importante para la innovación en el empaquetado de chips y las tecnologías de interconexión, según Guo Ping, presidente rotativo retirado de Huawei. A medida que las características en unidades más pequeñas, conocidas como «die», se reducen a 3 nanómetros y nodos aún más pequeños, el empaquetado en 3D, en particular, está evolucionando rápidamente y adquiriendo una mayor relevancia. En resumen, la integración en 3D engloba un espectro amplio de tecnologías, como el empaquetado en 3D a nivel de oblea, la integración basada en interpositores 2,5D y 3D, los chips 3D apilados (3D-SIC), los chips monolíticos 3D, la integración 3D heterogénea y la integración de sistemas 3D.