Actualizado a: 19 de enero de 2024

El 3D Packaging, o empaquetado 3D, es un concepto que ya hace unos años que se comenzó a diseñar y usar en algunos productos, pero que es ahora cuando más importancia se le está dando, dado que los chips monolíticos tienen serios problemas para seguir avanzando. Por eso, junto con los chiplets, este tipo de empaquetado puede seguir mejorando la tecnología en los años venideros.

¿Qué es el empaquetado de chips (2D packaging)?

En la fabricación de electrónica, el empaquetado de circuitos integrados (chip packaging) es la etapa final de la fabricación de dispositivos semiconductores, en la cual el chip (die) de material semiconductor se encapsula en una envoltura que sirve de soporte para prevenir daños físicos y corrosión, también actúa como soporte para los contactos eléctricos o pines para la comunicación con el exterior, actúa como sellado, etc.

Algunos tipos de encapsulados tienen dimensiones y tolerancias estandarizadas y están registrados en asociaciones de la industria comercial como JEDEC y Pro Electron. Otros tipos son designaciones propietarias, y usados solo por ciertos fabricantes para dispositivos concretos.

El packaging puede hacerse mediante distintas formas, dos de las más comunes son:

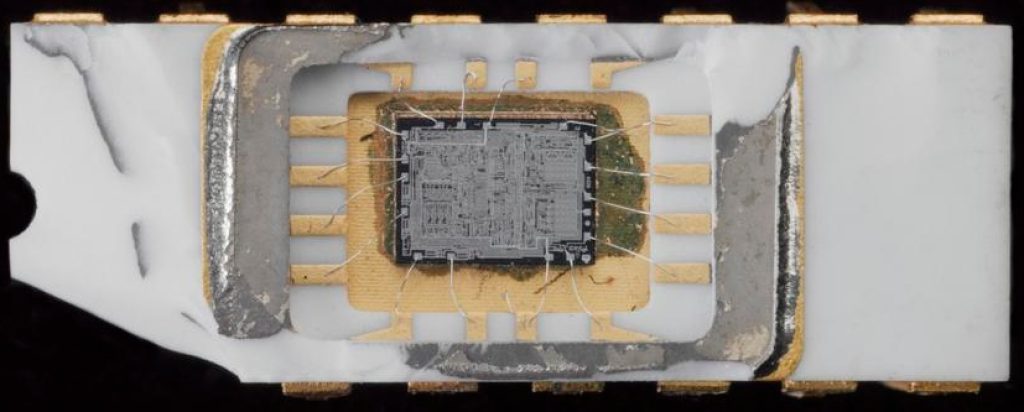

- Wire Bonding: es un proceso de unión en el que se conectan los terminales de un chip semiconductor a través de alambres delgados de oro o aluminio con puntos de conexión en la placa de circuito impreso (PCB) u otros chips. Hay dos tipos principales de wire bonding, uno por ultrasonidos para fundir el metal, y otro mediante termocompresión. Wire bonding es una técnica versátil que se utiliza en una variedad de aplicaciones, especialmente en chips de montaje superficial (SMD) y circuitos integrados de dispositivos electrónicos convencionales.

- Flip-Chip: es una técnica de montaje en la que el chip semiconductor se coloca boca abajo (con sus contactos hacia abajo) y se conecta directamente a la PCB u otro sustrato mediante soldadura o conexiones tipo BGA (aunque luego el sustrato termine siendo PGA o LGA…). Esta técnica ofrece ventajas como una mayor densidad de pines, mejor disipación de calor y una ruta de señal más corta, lo que puede mejorar el rendimiento y la velocidad de los dispositivos. Por eso se emplea en dispositivos avanzados como microprocesadores, GPUs, memoria, etc. Además, hay que diferenciar entre Bare Die FC y CSP o Chip Scale Package. En la primera técnica el chip se coloca directamente sobre la PCB y se suelda. En el segundo caso se coloca sobre un sustrato, se suelda y luego se cubre con su encapsulado. Los contactos en este caso estarán en la parte inferior (PGA, LGA o BGA).

Una vez realizado esto, el chip no está terminado, luego se procede a realizar otros procesos de encapsulación como el horneado para el endurecimiento del material, el plating, el marcado mediante láser (lasermarking) para grabarlo las letras que suelen tener en su superficie, etc. Y una vez finalizado, se realizan tests para verificar que funcionan bien…

Algunos tipos de empaquetado

Existen gran cantidad de tipos de packaging o empaquetados, como por ejemplo:

- COB (Chip on Board): se trata de un chip directamente soldado a la placa PCB y con un tipo resina epoxy protectora. Es muy habitual verlo en dispositivos electrónicos baratos, como pueden ser las calculadoras.

- SIP (Single In-line Package): contiene una fila de pines en un solo lado y se utiliza en aplicaciones donde el espacio es limitado.

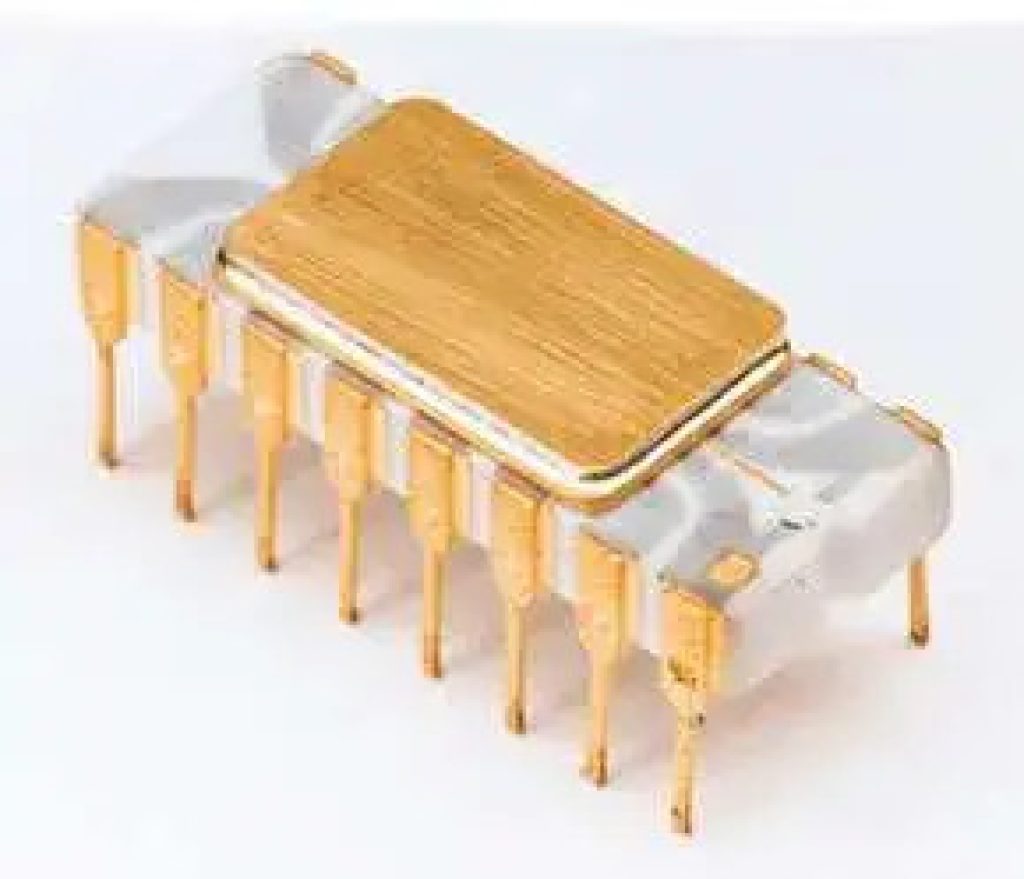

- DIP (Dual In-Line Package): Este es un envase rectangular con pines en ambos lados que se insertan en un zócalo o se sueldan a una placa de circuito impreso. Suele ser de plástico en la mayoría de los casos, aunque también hay de cerámica, como CDIP, para mayor durabilidad y disipación de calor.

- ZIP ( Zig-Zag In-line Package): similar al DIP, pero con pines dispuestos en zigzag para ahorrar espacio.

- PLCC (Plastic Leaded Chip Carrier): un encapsulado cuadrado o rectangular con pines en los cuatro lados que se utilizan en aplicaciones donde se requiere una mayor densidad de pines. Generalmente también es de plástico, aunque puede haber otros materiales.

- PGA (Pin Grid Array): similar al LGA, pero con pines más en vez de pads, y se conecta al zócalo del PCB que es el que tiene los orificios y los pads de contacto. Es decir, es al contrario. Esto puede hacer más vulnerable al chip si se doblan o pierden los pines de contacto, pero también tiene sus ventajas. Existen variantes como OPGA (Organic PGA) de material orgánico, FCPGA (Flip-chip PGA) cuyo chip no se conecta mediante wire bonding, PAC (Pin Array Cartridge), CPGA (Ceramic PGA) de cerámica, PPGA (Plastic PGA), etc.

- BGA (Ball Grid Array): similar al anterior, pero usa esferas o bolas en vez de pines de contacto. Además, irá soldado a la superficie de la PCB. Es común ver este tipo de empaquetado para los procesadores o GPUs para portátiles. También existen variantes como FBGA (Fine-pitch BGA) para su soldado en superficie donde la delgadez es importante, LBGA (Low-profile BGA), OBGA, CBGA, PBGA, etc.

- LGA (Land Grid Array): los contactos o pads se encuentran en una matriz en la parte inferior del chip, y se conectan al socket o zócalo del PCB, que es el que tiene los pines. Ejemplos de este tipo de empaquetado son los Intel Core, AMD Threadripper, etc. Generalmente se usa en chips muy avanzados con un gran recuento de contactos. En este caso también puede haber variantes según el material, como en los dos casos anteriores.

- MCM (Multi-Chip Module): alberga múltiples chips en un solo paquete y permite la integración de componentes en un espacio reducido. Es decir, está pensado para los denominados chiplets.

- PQFP (Plastic Quad Flat Package): es plano y cuadrado con pines en todos los lados, utilizado en aplicaciones de alta densidad.

- SOP (Small Outline Package): rectangular de perfil bajo con pines en dos lados que se utiliza para ahorrar espacio en la PCB.

- SOIC (Small Outline Integrated Circuit): similar al SOP, pero con pines en dos lados y encapsulado en plástico.

- TSOP (Thin Small Outline Package): similar al SOIC, pero con una carcasa más delgada para ahorrar espacio y mejorar la disipación de calor.

Estos son solo algunos de los tipos de envases de chips más comunes, y hay muchos otros diseñados para satisfacer requisitos específicos de aplicaciones y diseño.

POP (Package on Package)

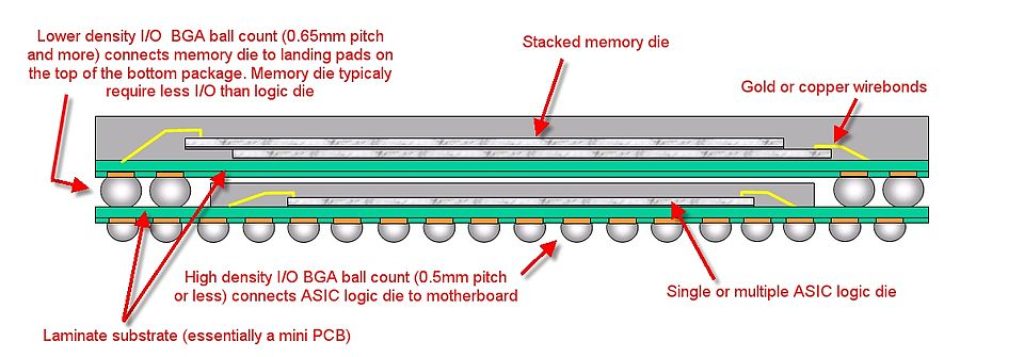

También hay que diferenciar lo que es el Package on a Package (PoP). En este caso se trata de un método de empaquetado de circuitos integrados que combina verticalmente empaquetados de lógica discreta y memoria con una disposición BGA. Es decir, no es un 3D packaging, sino que directamente se apilan chips ya empaquetados por separado.

Durante el ensamblaje de la PCB, el paquete inferior de una pila PoP se coloca directamente en la PCB, y los demás paquetes de la pila se apilan encima. Los paquetes de una pila PoP quedan unidos entre sí durante la soldadura por reflujo.

Esto permite una mayor densidad de componentes en dispositivos como teléfonos móviles, cámaras digitales, etc.

Por otro lado, es importante destacar que existen dos configuraciones posibles para PoP:

- Pure Memory Stacking: se apilan dos o más empaquetados de memoria uno encima del otro.

- Mixed Logic-memory Stacking: se apilan empaquetados de lógica y memoria en un mismo empaquetado final. Por ejemplo, se podría usar un empaquetado de CPU junto a chips de memoria DRAM. En estos casos, el empaquetado de lógica está en la parte inferior, ya que es el que más conexiones BGA necesita.

¿Qué es el 2.5D packaging?

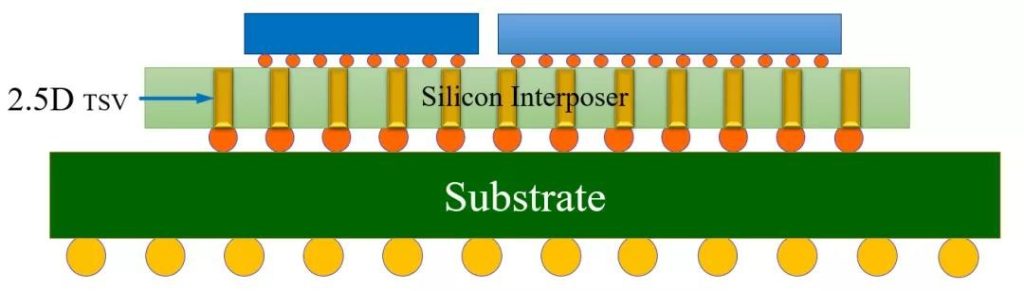

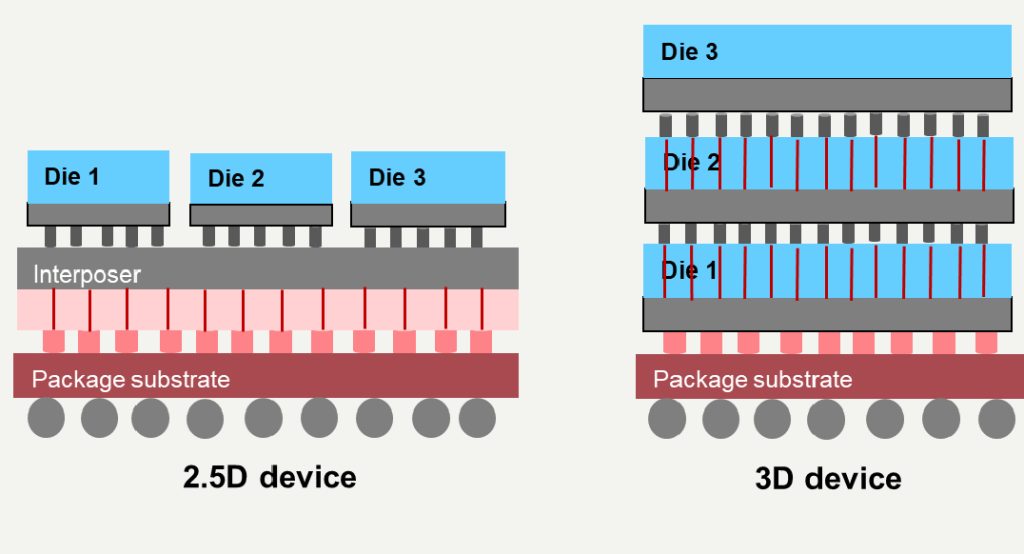

Un circuito integrado 2.5D (2.5D IC) es una técnica avanzada de empaquetado que combina múltiples obleas de chips en un solo empaquetado, sin apilarlos como ocurre en el 3D. Los diseñadores de chips se dieron cuenta de que muchas de las ventajas de la integración 3D podían aproximarse al colocar obleas desnudas una al lado de la otra en un interposador en lugar de apilarlas verticalmente.

Si la distancia entre chips es muy pequeña y la interconexión es muy corta, el conjunto puede empaquetarse como un solo componente con mejores características de tamaño, peso y consumo de energía e incluso mayor rendimiento debido a la menor latencia frente a distintos empaquetados 2D convencionales que están conectados mediante una PCB.

Ventajas del 2.5D packaging

Algunas ventajsa de este tipo de empaquetado son:

- Un interposer puede admitir una integración heterogénea en chiplets, es decir, obleas de diferentes distancias entre pines, tamaños, materiales y nodos de proceso.

- Incluso puede aumentar el yield frente a otros diseños 3D.

- Permite empaquetar chips muy cerca los unos de los otros, con ventajas en cuanto a tamaño, latencia de señales, eficiencia energética, etc., aunque no igualan a los chips monolíticos.

¿Qué es el 3D packaging? El empaquetado 3D

Los chips empaquetados se disponen en la placa de circuito y se conectan entre sí mediante diminutos cables. En todos los tipos de empaquetado 3D (3D packaging), los chips dentro de un mismo paquete se comunican utilizando señales fuera del chip, como si estuvieran en paquetes separados en una placa de circuito normal. Algunos chips 3D, como las memorias HBM y las CPUs de Intel, utilizan microbobinas de cobre muy pequeñas para las conexiones internas junto con el proceso de volteo del chip.

Una técnica llamada Hybrid Binding, apila y conecta los chips utilizando conexiones de cobre a cobre extremadamente pequeñas, lo que ofrece una mayor densidad y rendimiento en comparación con los métodos de interconexión de chips apilados actuales. La unión híbrida de cobre, una tecnología relativamente nueva en la fabricación de semiconductores, es una tecnología líder en el apilamiento de chips que promete ventajas competitivas para los clientes de chips. Los primeros chips que utilizan esta tecnología, conocida como «hybrid bonding», están allanando el camino para una nueva era competitiva de productos de chips basados en 3D y envases avanzados.

AMD fue el primer fabricante en introducir chips con «hybrid bonding», una tecnología de vanguardia para el apilamiento de chips que permite la próxima generación de dispositivos y empaquetados 3D. Esta tecnología ofrece nuevas opciones para diseños de alta gama y abre la puerta a la próxima generación de diseños en 3D, en matrices de RAM, memoria flash, y otros chips más avanzados, como los heterogéneos.

En este contexto, la tecnología de interconexión determina cómo se apilan y unen las matrices en los paquetes, es decir, los chips semiconductores. En un circuito electrónico tradicional en 2D, cada matriz se empaqueta de forma individual. Las pilas de matrices en los chips 3D están mucho más cerca que en un circuito impreso convencional.

El diseño del chip debe considerar el apilamiento de chips y se requiere maquinaria especializada para alinearlos y unirlos. Cada matriz en una pila debe diseñarse específicamente para el apilamiento, lo que implica un esfuerzo de diseño importante. Las pilas de varios chips pueden incluir combinaciones que simplemente no serían posibles en chips 2D.

¿Qué es TSV?

Through-Silicon Via (TSV) es una conexión eléctrica vertical que atraviesa completamente una oblea de silicio o chip. Los TSV son técnicas de interconexión de alto rendimiento utilizadas para interconectar chips apilados en el 3D packaging.

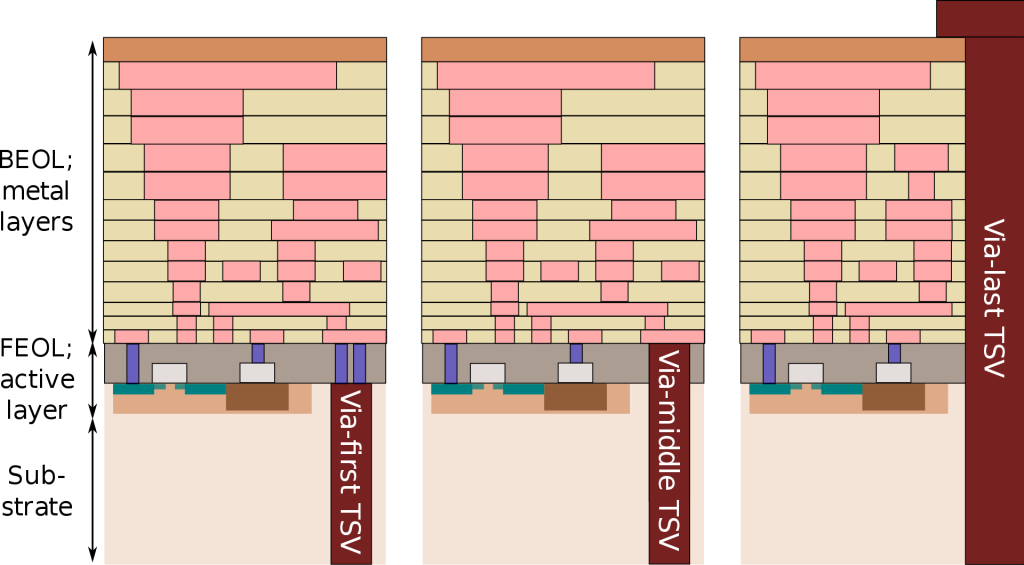

Existen tres tipos diferentes de TSVs:

- Via-first TSV: se fabrican antes de que los elementos individuales (transistores, condensadores, resistencias, etc.) sean modelados (front end of line, FEOL). Los TSV durante el FEOL deben tenerse en cuenta durante las fases de diseño EDA y fabricación, ya que los TSV inducen estrés termomecánico en la capa FEOL, lo que afecta el comportamiento del transistor.

- Via-middle TSV: se fabrican después de que los componentes individuales son modelados pero antes de las capas metálicas de interconexiones (back-end-of-line, BEOL). Esta suele ser una de las opciones más utilizadas en la actualidad.

- Via-last TSV: se fabrican después (o durante) el proceso BEOL.

Tipos de empaquetado 3D

En el contexto de la integración tridimensional, existen tres tipos fundamentales:

- Empaquetado 3D (3D Packaging): este enfoque utiliza métodos tradicionales de interconexión, como el wire bonding y el flip chip, para lograr el apilamiento vertical de componentes. Se divide en dos categorías:

- System-in-Package (3D SiP): implica la interconexión de matrices de memoria apiladas mediante wire bonds o tecnología flip chip.

- Wafer Level Packaging (3D WLP): utiliza procesos a nivel de oblea, como capas de redistribución (RDL) y procesos de bumping de la oblea, para formar las interconexiones.

- Interconexión 2.5D (Interposer 2.5D): ya la he descrito anteriormente, es una variante del WLP, usando TSVs (Through Silicon Vias) y una capa de redistribución o interposer. Para más información, véase el apartado anterior.

- Circuitos Integrados 3D (3D ICs): estos se dividen en dos tipos principales:

- 3D Stacked IC (3D SIC): implica el apilamiento de chips utilizando interconexiones a través de TSVs.

- 3D Monolithic IC: que utilizan procesos de fabricación en capas en una sola oblea de silicio, lo que resulta en interconexiones verticales directas entre las capas de dispositivos. Los dispositivos de memoria NAND Flash en dispositivos móviles son ejemplos de la amplia aplicación de empaquetados 3D IC.

Cómo se fabrican

Existen varios métodos para el diseño de 3D, que incluyen métodos de recristalización y métodos de unión de obleas. Dos tipos principales de unión de obleas son las conexiones Cu-Cu (conexiones de cobre a cobre entre circuitos integrados apilado) y las conexiones a través de silicio (TSV). Estos métodos que debes ocnocer son:

- Die-to-Die: los chips se construyen en múltiples obleas que luego se alinean y unen. El adelgazamiento y la creación de TSV pueden realizarse antes o después de la unión. Una ventaja de este enfoque es que cada oblea de componente puede ser probada por separado, lo que evita que una oblea defectuosa arruine todo el apilamiento. Además, cada oblea en el 3D IC puede ser clasificada de antemano para optimizar el consumo de energía y el rendimiento (binning).

- Die-to-Wafer: los chips se construyen en dos obleas de semiconductor. Una oblea se divide en chips, que se alinean y unen en los chips aún unidos de la segunda oblea. Al igual que en el método Wafer-to-Wafer, el adelgazamiento y la creación de TSV se realizan antes o después de la unión. Incluso se pueden agregar chips adicionales antes del corte final.

- Wafer-to-Wafer: los chips se fabrican en dos o más obleas de semiconductor, que luego se alinean, unen y dividen en chips. Cada oblea puede adelgazarse antes o después de la unión. Las conexiones verticales se construyen en las obleas antes de la unión o se crean en la pila después de la unión mediante TSVs, que atraviesan el sustrato de silicio entre las capas activas y/o entre una capa activa y una almohadilla de unión externa. La unión de oblea a oblea puede reducir el yield, ya que si uno de N chips está defectuoso, todo el 3D IC será defectuoso, es decir, toda la pila. Además, las obleas deben ser del mismo tamaño, lo que puede complicar la integración heterogénea, especialmente cuando se usan materiales exóticos en obleas más pequeñas que las obleas de lógica CMOS o DRAM convencionales (generalmente de 300 mm).

Ventajas y retos que superar

Como cualquier tecnología, es lógico que se encuentre algunas ventajas frente a los empaquetados 2D convencionales. Y estos beneficios son:

- Espacio: permite que más funcionalidades y chips por unidad de superficie.

- Coste: se pueden dividir un chip grande en múltiples obleas más pequeñas con apilamiento en 3D puede mejorar el yield y reducir los costes de fabricación si se prueban las obleas individualmente.

- Integración Heterogénea: las capas de circuitos pueden construirse con diferentes procesos o incluso en diferentes obleas, lo que permite una optimización mucho mayor de los componentes que si se construyeran juntos en una sola oblea, e incluso usando obleas con distintos materiales (Si, Si-Ge,…).

- Interconexión más Corta: se reduce la longitud promedio de las interconexiones, lo que disminuye la latencia en el circuito y puede mejorar la eficiencia.

- Consumo de energía: mantener una señal en el chip puede reducir su consumo de energía significativamente, en comparación con tener que comunicar distintos empaquetados que generalmente están más lejos.

- Seguridad del circuito: la estructura apilada complica los intentos de ingeniería inversa. Además, permite integrar características de seguridad en capas separadas.

- Ancho de banda: permite construir buses de ancho de banda amplio entre bloques funcionales en diferentes capas, lo que puede resolver el problema de la «pared de memoria».

La tecnología 3D IC también presenta desafíos que hay que resolver para poderla usar masivamente en un futuro, como:

- Coste: el proceso de empaquetado es más complejo y cuesta más que los empaquetados convencionales.

- Yield: cada paso de fabricación adicional aumenta el riesgo de defectos, lo que puede afectar la rentabilidad.

- Calor: la acumulación de calor dentro del apilamiento debe disiparse adecuadamente, algo que podría implicar nuevos sistemas de refrigeración.

- Complejidad del diseño: aprovechar al máximo la integración en 3D requiere técnicas de diseño sofisticadas y nuevas herramientas CAD/EDA.

- Sobrecarga introducida por TSV: las conexiones a través de silicio son grandes en comparación con las interconexiones o los transistores, y afectan los diseños de chips apilados. Es decir, necesitan superficie adicional para su creación.

- Pruebas: además de las pruebas de obleas individuales, en este caso también se necesita probar los chips empaquetados una vez se han apilado, para ver que funcionan adecuadamente.

- Falta de Estándares: la falta de estándares en el diseño, fabricación y 3d packaging es un desafío, aunque se está trabajando en abordar este problema.

- Propiedad no Definida: no está claro quién debe ser el dueño de la integración y el ensamblaje de 3D IC, ya que los chips u obleas pueden provenir de fabricantes muy diferentes. Por ejemplo, chips de memoria de Samsung junto a chips de procesamiento de AMD, etc.

Tecnologías para el 3D Packaging

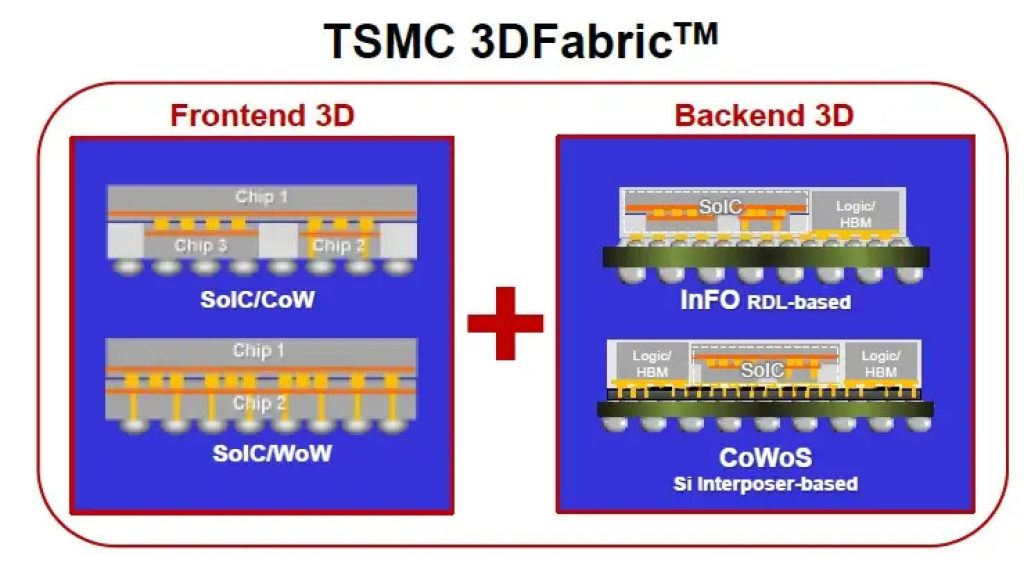

En la actualidad, al no ser una técnica de fabricación demasiado madura, y no tener estandarización, como he comentado anteriormente, cada compañía está desarrollando sus tecnologías, aunque todas son muy similares a grandes rasgos. Por ejemplo, TSMC, Intel y Samsung tienen las suyas propias.

Para más información sobre las tecnologías actuales, te invito a leer este otro artículo.